Network and Remote Operation

R&S

®

FSVA3000/ R&S

®

FSV3000

676

User Manual 1178.8520.02 ─ 01

STATus:QUEStionable:LIMit Register

The STATus:QUEStionable:LIMit register contains information about the results of a

limit check when you are working with limit lines.

A separate LIMit register exists for each active channel and for each window.

You can read out the register with

STATus:QUEStionable:LIMit<n>:CONDition?

or

STATus:QUEStionable:LIMit<n>[:EVENt]?

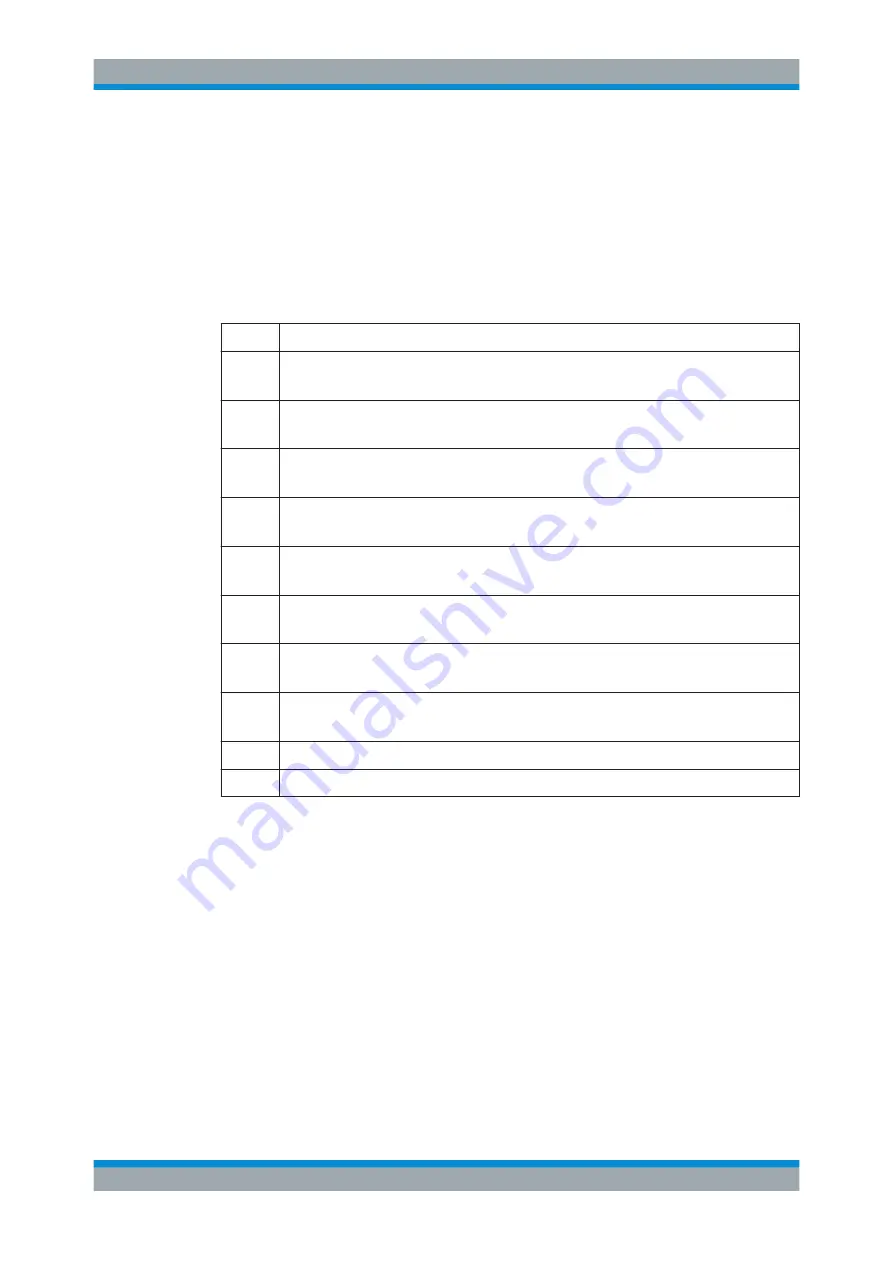

Table 13-15: Meaning of the bits used in the STATus:QUEStionable:LIMit register

Bit No.

Meaning

0

LIMit 1 FAIL

This bit is set if limit line 1 is violated.

1

LIMit 2 FAIL

This bit is set if limit line 2 is violated.

2

LIMit 3 FAIL

This bit is set if limit line 3 is violated.

3

LIMit 4 FAIL

This bit is set if limit line 4 is violated.

4

LIMit 5 FAIL

This bit is set if limit line 5 is violated.

5

LIMit 6 FAIL

This bit is set if limit line 6 is violated.

6

LIMit 7 FAIL

This bit is set if limit line 7 is violated.

7

LIMit 8 FAIL

This bit is set if limit line 8 is violated.

8 to 14

Unused

15

This bit is always 0.

STATus:QUEStionable:LMARgin Register

This register contains information about the observance of limit margins.

A separate LMARgin register exists for each active channel and for each window.

It can be read using the commands

STATus:QUEStionable:LMARgin:CONDition?

and

STATus:QUEStionable:LMARgin[:EVENt]?

.

Remote Control Basics