Remote control

R&S

®

ZNB/ZNBT

833

User Manual 1173.9163.02 ─ 62

STATus:QUEStionable:LIMit<1|2>[:EVENt]?

STATus:QUEStionable:LIMit1

is also the summary register of the lower level

STATus:QUEStionable:LIMit2

register.

The bits in the

STATus:QUEStionable:LIMit1

register are defined as follows:

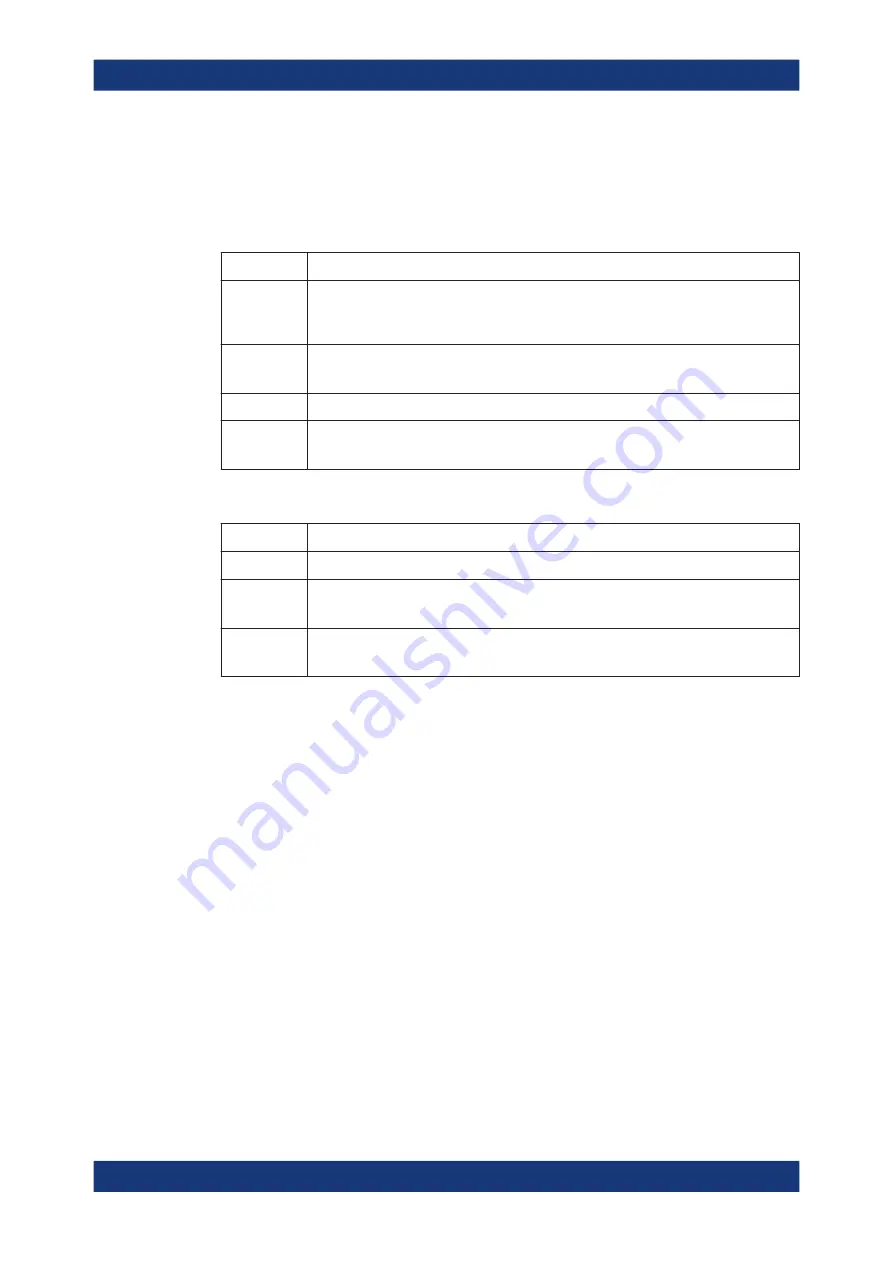

Bit No.

Meaning

0

LIMit2 register summary

This bit is set if a bit is set in the STATus:QUEStionable:LIMit2 register and the associated

ENABle bit is set to 1.

1

Failed limit check for trace no. 1

This bit is set if any point on trace no. 1 fails the limit check.

...

...

14

Failed limit check for trace no. 14

This bit is set if any point on trace no. 14 fails the limit check.

The bits in the

STATus:QUEStionable:LIMit2

register are defined as follows:

Bit No.

Meaning

0

Not used

1

Failed limit check for trace no. 15

This bit is set if any point on trace no. 15 fails the limit check.

2

Failed limit check for trace no. 16

This bit is set if any point on trace no. 16 fails the limit check.

Numbering of traces

The traces numbers 1 to 16 are assigned as follows:

●

Traces assigned to channels with smaller channel numbers have smaller trace

numbers.

●

Within a channel, the order of traces reflects their creation time: The oldest trace

has the smallest, the newest trace has the largest trace number. This is equivalent

to the order of traces in the response string of the

CALCulate<Ch>:PARameter:CATalog?

query.

●

The number of traces monitored cannot exceed 16. If a setup contains more

traces, the newest traces are not monitored.

STATus:QUEStionable:INTegrity...

The

STATus:QUEStionable:INTegrity

register monitors hardware failures of the

analyzer. It can be queried using the commands

STATus:QUEStionable:INTegrity:CONDition?

or

STATus:QUEStionable:INTegrity[:EVENt]?

STATus:QUEStionable:INTegrity

is also the summary register of the lower level

STATus:QUEStionable:INTegrity:HARDware

register.

Status reporting system