Publication No. REF-000-009-R00

Red Rapids

Page 2

2.0 Description

The Front End 000-009 receiver is a high performance dual-channel structure built around

the Analog Devices AD9652 16 bit 310 Msps dual ADC.

Features

1

:

Dual Channel

16-bit Architecture

SNR 75 dB

SFDR 94 dB

Sample Rate up to 310 Msps

PGA Front End (2.0 Vpp or 2.5 Vpp Input)

3-Pole Chebyshev or Butterworth lowpass input filter (optional)

400 MHz Full Power Bandwidth

AC or DC Coupled (Build option)

Precision DC offset adjustment (DC-Coupled option)

Note

1

: Features listed are mode and build dependent. See specifications and

performance sections for more information.

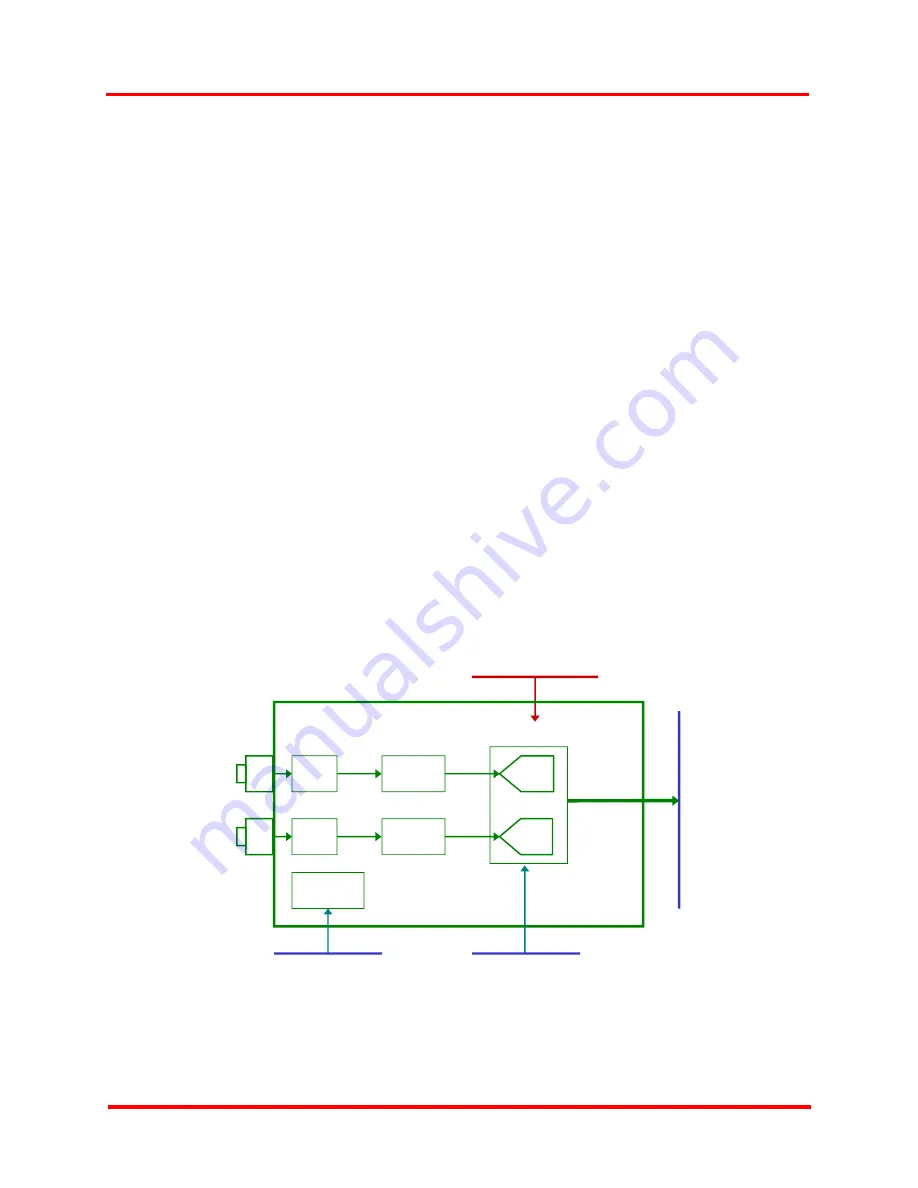

A block diagram of the receiver is shown in Figure 2-1. The receiver consists of two

independent analog input channels labeled 1 and 2. A receiver channel consists of a front

panel SMA connector, an optional signal conditioning filter and a coupling mechanism (AC

or DC) that bridges the analog input to the ADC. Analog inputs are digitized by a dual

ADC that creates discrete data samples and streams them to the data Interface using a

high-speed precision clock distributed from a low noise network.

The following paragraphs provide details about each element of the receiver section.

Receiver

Data

Interface

Clock

Interface

DC Offset

Adjust

Control Interface

Control Interface

ADCB

RX 2

SM

A

SM

A

RX 1

ADCA

RX 1, RX 2

Coupling

Filter

Coupling

Filter

Dual ADC

Interleaved

Figure 2-1 Receiver Block Diagram