CHAPTER 15 SERIAL INTERFACE IICA

Page 499 of 920

15.6

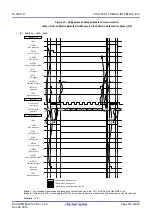

Timing Charts

When using the I

2

C bus mode, the master device outputs an address via the serial bus to select one of several slave

devices as its communication partner.

After outputting the slave address, the master device transmits the TRCn bit (bit 3 of the IICA status register n

(IICSn)), which specifies the data transfer direction, and then starts serial communication with the slave device.

Figures 15 - 40 to 15 - 46 show timing charts of the data communication.

The IICA shift register n (IICAn)’s shift operation is synchronized with the falling edge of the serial clock (SCLAn).

The transmit data is transferred to the SO latch and is output (MSB first) via the SDAAn pin.

Data input via the SDAAn pin is captured into IICAn at the rising edge of SCLAn.

Remark

n = 0, 1

Summary of Contents for RL78/G1H

Page 941: ...R01UH0575EJ0120 RL78 G1H...