CHAPTER 15 SERIAL INTERFACE IICA

Page 513 of 920

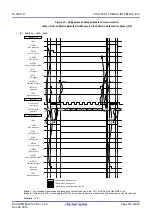

The meanings of <8> to <19> in (3) Data ~ data ~ stop condition in Figure 15 - 46 are explained below.

<8> The master device sets a wait status (SCLAn = 0) at the falling edge of the 8th clock, and issues an interrupt

(INTIICAn: end of transfer). Because of ACKEn = 0 in the master device, the master device then sends an ACK

by hardware to the slave device.

<9> The master device reads the received data and releases the wait status (WRELn = 1).

<10>The ACK is detected by the slave device (ACKDn = 1) at the rising edge of the 9th clock.

<11>The slave device set a wait status (SCLAn = 0) at the falling edge of the 9th clock, and the slave device issue

an interrupt (INTIICAn: end of transfer).

<12>By the slave device writing the data to transmit to the IICA register, the wait status set by the slave device is

released. The slave device then starts transferring data to the master device.

<13>The master device issues an interrupt (INTIICAn: end of transfer) at the falling edge of the 8th clock, and sets a

wait status (SCLAn = 0). Because ACK control (ACKEn = 1) is performed, the bus data line is at the low level

(SDAAn = 0) at this stage.

<14>The master device sets NACK as the response (ACKEn = 0) and changes the timing at which it sets the wait

status to the 9th clock (WTIMn = 1).

<15>If the master device releases the wait status (WRELn = 1), the slave device detects the NACK (ACKDn = 0) at

the rising edge of the 9th clock.

<16>The master device and slave device set a wait status (SCLAn = 0) at the falling edge of the 9th clock, and both

the master device and slave device issue an interrupt (INTIICAn: end of transfer).

<17> When the master device issues a stop condition (SPTn = 1), the bus data line is cleared (SDAAn = 0) and the

master device releases the wait status. The master device then waits until the bus clock line is set (SCLAn = 1).

<18> The slave device acknowledges the NACK, halts transmission, and releases the wait status (WRELn = 1) to

end communication. Once the slave device releases the wait status, the bus clock line is set (SCLAn = 1).

<19> Once the master device recognizes that the bus clock line is set (SCLAn = 1) and after the stop condition setup

time has elapsed, the master device sets the bus data line (SDAAn = 1) and issues a stop condition (i.e. SCLAn

=1 changes SDAAn from 0 to 1). The slave device detects the generated stop condition and slave device issue

an interrupt (INTIICAn: stop condition).

Remark 1.

<1> to <19> in Figures 15 - 44 to 15 - 46 represent the entire procedure for communicating data

using the I

2

C bus. Figure 15 - 44 (1) Start condition ~ address ~ data shows the processing from

<1> to <7>, Figure 15 - 45 (2) Address ~ data ~ data shows the processing from <3> to <12>, and

Figure 15 - 46 (3) Data ~ data ~ stop condition shows the processing from <8> to <19>.

Remark 2.

n = 0, 1

Summary of Contents for RL78/G1H

Page 941: ...R01UH0575EJ0120 RL78 G1H...