Hardware Design Specification

ASD-B-16-0247 Rev1.3

Page 33 of 105

September 8, 2017

RTK00V2XRC7746SFS

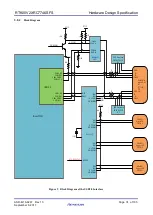

3.10.2

CPU JTAG2 debug

3.10.2.1

Specification

On the Tethys board,

t

he R-Car W2H has the CPU JTAG2 debug interface. The SW12 switch 2-3 short is for normal operation

and 2-1 short for CPU JTAG2 debug

Table 13 CPU JTAG2 debug

Control Interface

CPU JTAG2

Debug Interface

CN4:

IMSA-9632S-26Y801 from IRISO

operating conditions

The SW12 switch 2-1 short

The SW1 switch 9-8 short, switch 10-7 short

The SW2 switch 8-1 short, switch 7-2 short, switch 6-3 short, switch 5-4 short

3.10.2.2

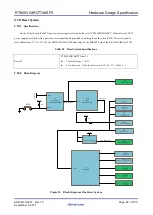

Block Diagram

D1.8V

10K

R-Car W2H

U1

JTAG CN

CN4

D1.8V

10K

10K

SW12

3

1

2

MMC0_CMD_TRST

MMC0_D2_TDI

MMC0_D1_TMS

MMC0_D0_TCK

MMC0_D3_ASEBRK#/ACK

MMC0_CLK_TDO

5

4

3

6

7

2

8

1

SW2

9

10

8

7

SW1

GP0_15/MMC0_D0

GP0_16/MMC0_D1

GP0_17/MMC0_D2

GP0_18/MMC0_D3

GP0_13/MMC0_CLK

GP0_14/MMC0_CMD

Figure 11 Block Diagram of the CPU JTAG2 (SH-4AL) debug

Summary of Contents for RTK00V2XRC7746SFS

Page 110: ...RTK00V2XRC7746SFS ...