Hardware Design Specification

ASD-B-16-0247 Rev1.3

Page 35 of 105

September 8, 2017

RTK00V2XRC7746SFS

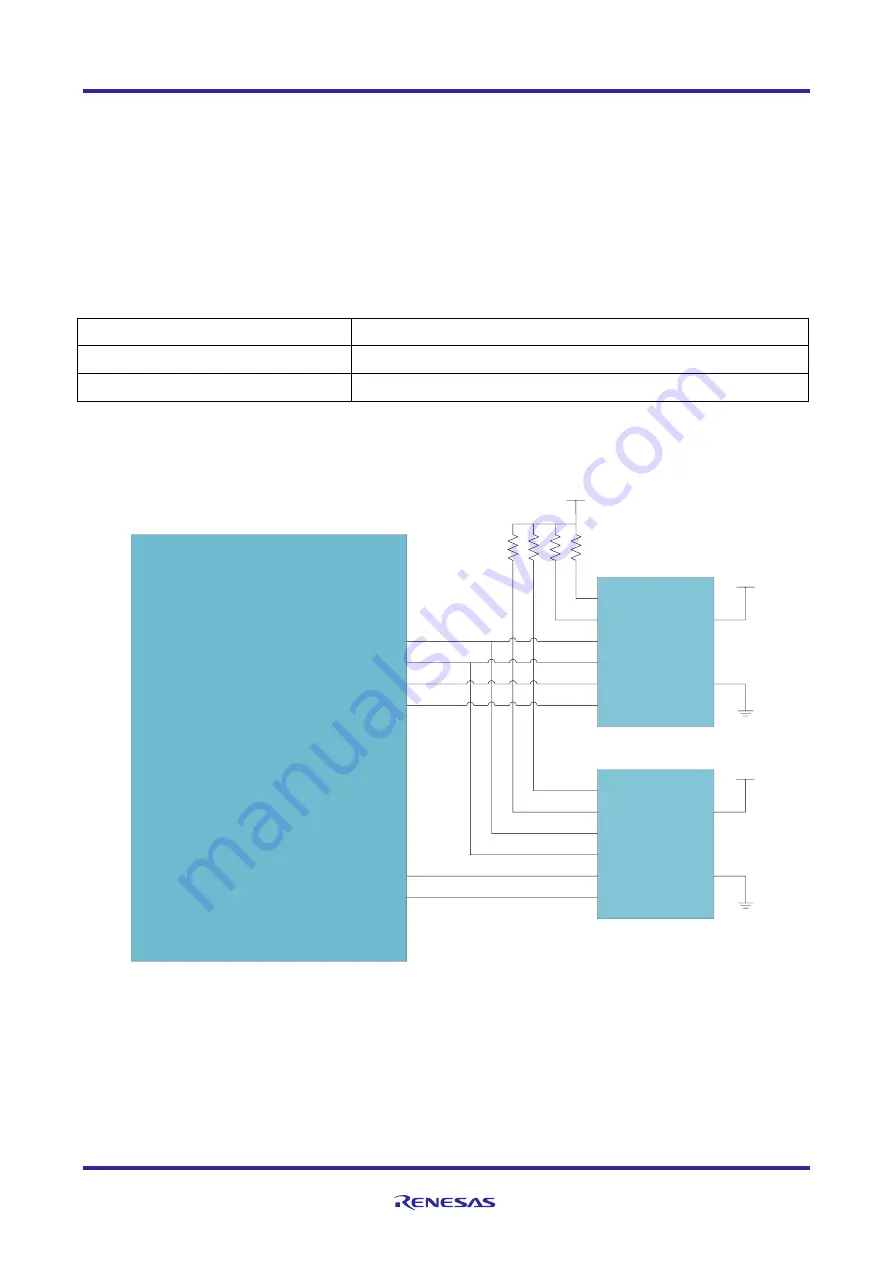

3.11

GYRO/G-SENSOR

3.11.1

Specifications

The A3G4250D manufactured by ST is a low-power 3-axis angular rate sensor able to provide unprecedented stability at zero

rate level and sensitivity over temperature and time. The AIS328DQ is an ultra low-power high performance 3-axis linear

accelerometer. The CPU communicates with the A3G4250D and AIS328DQ through its I2C1 and GPIOs.

Table 15 GYRO/G-SENSOR Specifications

Controller

R-Car W2H

Control Interface

The A3G4250D and AIS328DQ from ST

Supply voltage

D3.3V=3.3V

3.11.2

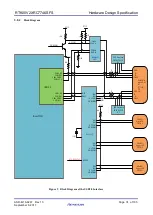

Block Diagram

SDO/SA0

CS

SCL

SDA

DRDY/INT2

INT1

SDO/SA0

CS

SCL

SDA

INT1

INT2

D3.3V

SCL1

SDA1

GP4_22

GP4_23

GP4_24

GP4_25

GYRO

A3G4250D

G-SENSOR

AIS328DQ

R-car W2H

10K

Figure 13 Block Diagram of the GYRO/G-SENSOR

Summary of Contents for RTK00V2XRC7746SFS

Page 110: ...RTK00V2XRC7746SFS ...