R01UH0823EJ0100 Rev.1.00

Page 1061 of 1823

Jul 31, 2019

RX23W Group

33. Serial Communications Interface (SCIg, SCIh)

33.7

Operation in Simple I

2

C Mode

Simple I

2

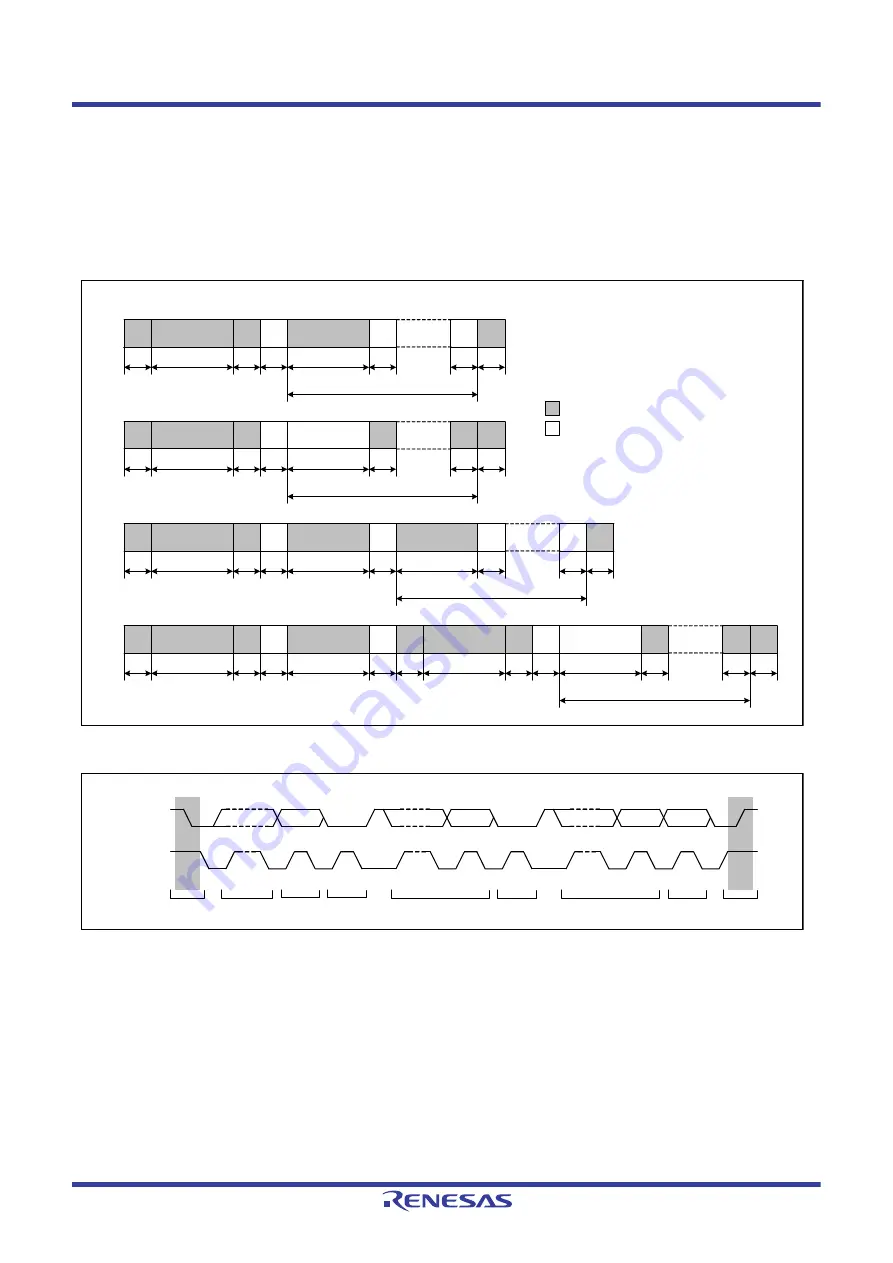

C-bus format is composed of 8 data bits and an acknowledge bit. By continuing into a slave-address frame after

a start condition or restart condition, a master device is able to specify a slave device as the partner for communications.

The currently specified slave device remains valid until a new slave device is specified or a stop condition is satisfied.

The 8 data bits in all frames are transmitted in order from the MSB.

The I

2

C-bus format and timing of the I

2

C-bus are shown in

.

Figure 33.46

I

2

C-bus Format

Figure 33.47

I

2

C-bus Timing (When SLA is 7 Bits)

S:

Indicates a start condition, i.e. the master device changing the level on the SSDAn line from the high to the low level while

the SSCLn line is at the high level.

SLA:

Indicates a slave address, by which the master device selects a slave device.

R/W#:

Indicates the direction of transfer (reception or transmission). The value 1 corresponds to transfer from the slave device

to the master device and 0 corresponds to transfer from the master device to the slave device.

A/A#:

Indicates an acknowledge bit. This is returned by the slave device for master transmission and by the master device for

master reception. Return of the low level indicates ACK and return of the high level indicates NACK.

Sr:

Indicates a restart condition, i.e. the master device changing the level on the SSDAn line from the high to the low level

while the SSCLn line is at the high level and after the setup time has elapsed.

DATA:

Indicates the data being received or transmitted.

P:

Indicates a stop condition, i.e. the master device changing the level on the SSDAn line from the low to the high level while

the SSCLn line is at the high level.

7-bit address format reception

S

SLA (7 bits)

R

A

DATA (8 bits)

A

A#

P

1

1

1

1

1

1

7

8

n (n = 1 or larger)

n: Number of transfer frames

10-bit address format transmission

S

SLA

(2 bits)

W#

A

SLA (8 bits)

1

1

1

7

8

A

DATA (8 bits)

A

A/A#

P

1

1

1

1

8

n (n = 1 or larger)

S

SLA

(2 bits)

W#

A

SLA (8 bits)

1

1

1

7

8

A

DATA (8 bits)

A

A#

P

1

1

1

1

8

n (n = 1 or larger)

Sr

SLA

(2 bits)

R

A

1

1

1

7

10-bit address format reception

7-bit address format transmission

S

SLA (7 bits)

W#

A

DATA (8 bits)

A

A/A#

P

1

1

1

1

1

1

7

8

n (n = 1 or larger)

: Master device

Slave device

: Slave device

Master device

SSDAn

SSCLn

1-7

8

9

1-7

8

9

S

SLA

R/W#

A

DATA

A

DATA

A

P

1-7

8

9

D7-D1

D0

D7-D1

D0

D7-D1

D0

MSB

LSB