R01UH0823EJ0100 Rev.1.00

Page 1081 of 1823

Jul 31, 2019

RX23W Group

33. Serial Communications Interface (SCIg, SCIh)

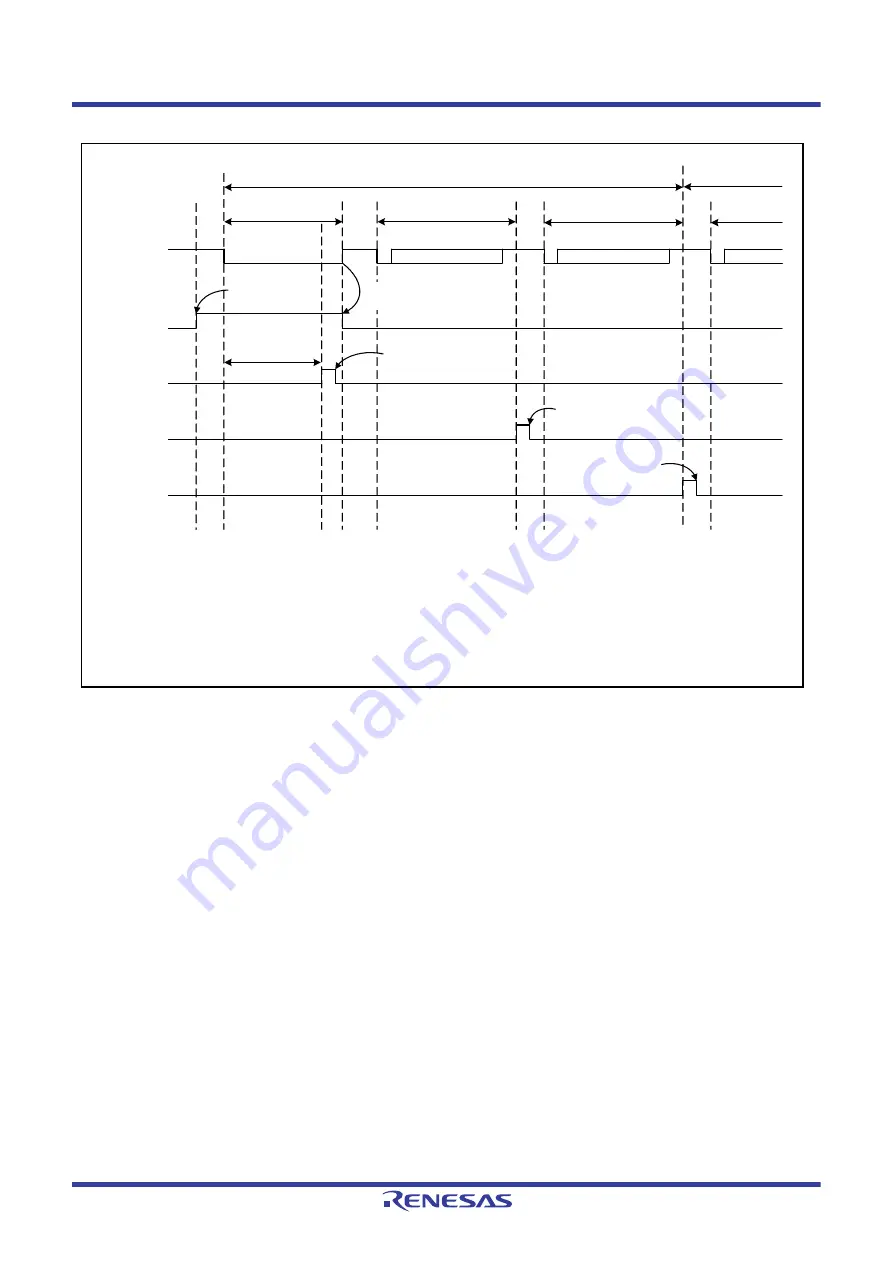

Figure 33.64

Example of Operations at the Time of Start Frame Reception

CR0.RXDSF

STR.BFDF

STR.CF0MF

STR.CF1MF

(1)

(2)

(3)

(4)

(5)

Control Field 0

8 bits

Control Field 1

8 bits

Break Field low width

Start Frame

Information Frame

Data Field

Write 1 to

CR3.SDST

Specified period for

TCNT and TPRE

Write 1 to

STCR.BFDCL

Write 1 to

STCR.CF0MCL

Write 1 to

STCR.CF1MCL

The above diagram assumes the following:

ESMER: ESME = 1

CR1:

BFE = 1, CF0RE = 1, CF1DS[1:0] = 10b

PCR:

RXDXPS = 0

ICR:

BFDIE = 1, CF0MIE = 1, CF1MIE = 1

TMR:

TOMS[1:0] = 01b

Set to 0 after Break Field

low width detection

RXDX12 pin