R01UH0823EJ0100 Rev.1.00

Page 1105 of 1823

Jul 31, 2019

RX23W Group

33. Serial Communications Interface (SCIg, SCIh)

33.14.12 Limitation 1 on Usage of the Extended Serial Mode Control Section

When the PCR.SHARPS bit is set to 1, output on the TXDX12/RXDX12 pin is only possible when the following

conditions apply.

The timer is in Break Field low width output mode and the value of the TCR.TCST bit is 1 (when the TCST bit is

set to 1, the high level continues to be output for up to one cycle of the clock source for counting by the timer

counter before output of the low level)

The value of the SCR.TE bit is 1.

33.14.13 Limitation 2 on Usage of the Extended Serial Mode Control Section

The TXI, RXI, ERI, and TEI interrupt requests are generated even if the extended serial mode is enabled. However, the

RXI interrupt should not be enabled during reception of a Start Frame because the extended serial mode control section

uses the receive data full signal.

To use the RXI interrupts during a reception of the Information Frame, use it in accordance with one of the following

procedures. When a receive error is detected, clear the receive error flag and initialize the extended serial mode control

section.

(1) Set the SCR.RIE bit to 0 to disable the output of interrupt requests. Check the error flags in the SSR register on

completion of the reception of a Start Frame, because an ERI interrupt is not generated if a receive error occurs.

After reception of the Start Frame is completed, set the SCR.RIE bit to 1 by the time the first byte of the Information

Frame is received.

(2) Set the SCR.RIE bit to 1 to disable RXI interrupts and enable ERI interrupts for ICU.

Clear the IRn.IR flag to enable the acceptance of RXI interrupts by ICU by the time the first byte of the Information

Frame is received after the completion of Start Frame reception.

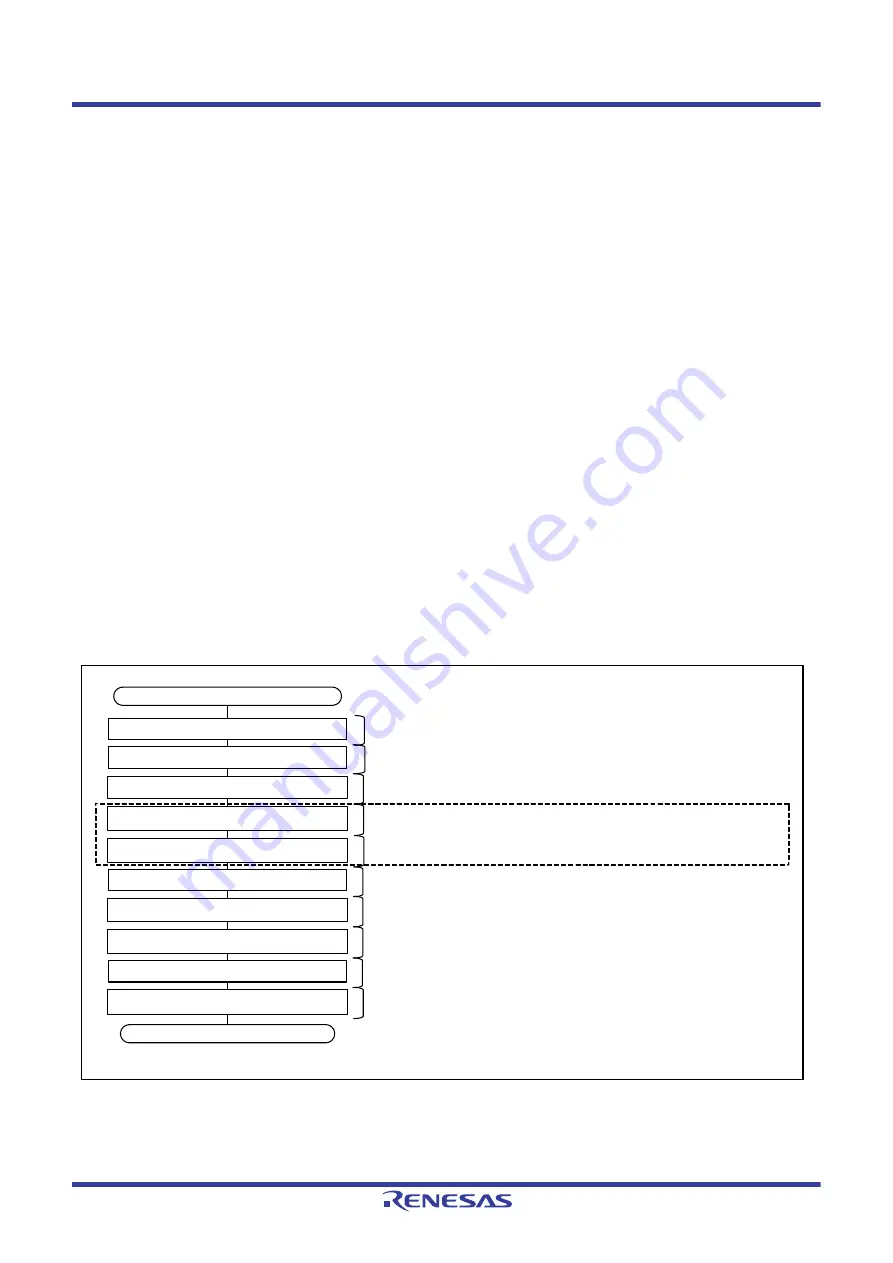

Figure 33.82

Example of Flowchart for Receive Error Handling (during Reception of the Start Frame)

Set the ESMER.ESME bit to 0

Set the TCR.TCST bit to 0

Set the TMR.TOMS[1:0] bits

Disable extended serial mode. The state of the extended serial mode control

section is initialized.

Stop counting by the timer.

Set Break Field low width determination mode as the timer’s operating mode.

Set all bits in STCR to 1

Set the AEDIE, BCDIE, CF1MIE, CF0MIE and

BFDIE bits in the ICR

Clear all flags in the STR register.

Set interrupt enable bits as required.

Set the CR3.SDST bit to 1

This starts detection of the Start Frame.

Set the ESMER.ESME bit to 1

Enable extended serial mode.

Set the TCR.TCST bit to 1

Start counting by the timer so that judgment of Break Fields is possible.

Start of receive error handling

Completion of receive error handling

Set the TMR.TCSS[2:0] bits, and TPRE and TCNT

registers

Set a counter clock source that is suitable for the Break Field low width determination

mode and set the TPRE and TCNT registers.

*

1

Note 1. The setting in this step is not necessary if the setting conditions

have not been changed.

Clear receive error flags to 0

Clear the receive error flags (ORER, FER and PER) in the SSR register to 0.