R01UH0823EJ0100 Rev.1.00

Page 1110 of 1823

Jul 31, 2019

RX23W Group

34. IrDA Interface

34.3

Operation

34.3.1

Transmission

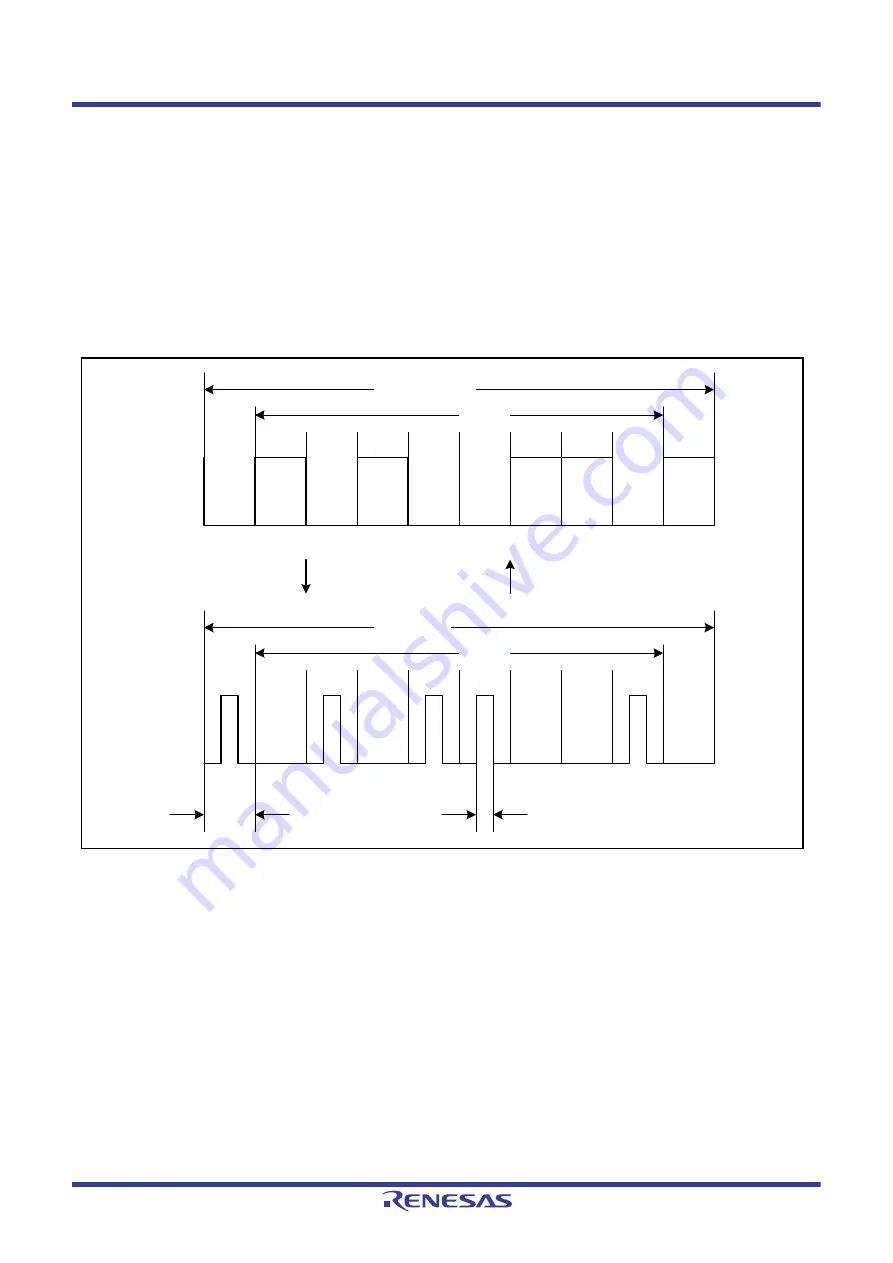

In transmission, the signals output from the SCI5 (UART frames) are converted to the IR frame data through the IrDA

interface (see

). When the IRCR.IRTXINV bit is 0 and data is 0, high-level pulses with 3/16 of the bit period

are output (initial setting). The high-level pulse width can be changed by setting the IRCR.IRCKS[2:0] bits. The standard

prescribes that the minimum high-level pulse width should be 1.41 μs and the maximum high-level pulse width should

be the bit period × (3/16 + 2.5%) or (the bit period × 3/16) + 1.08 μs. When the peripheral module clock PCLK is 20

MHz, the minimum high-level pulse width can be set to 1.6 μs (101b: PCLK/32) as shown in

. When data is

1, no pulses are output.

Figure 34.2

IrDA Transmission/Reception

UART frame

Data

0

1

0

1

0

0

1

1

0

1

Start bit

Stop bit

1

1

1

1

1

0

0

0

0

0

IR frame

Data

Start bit

Stop bit

Bit period

The pulse width is 1.4 µs to

the bit period x (3/16 + 2.5%)

or (the bit period × 3/16) + 1.08 µs

Transmission

Reception