R01UH0823EJ0100 Rev.1.00

Page 1317 of 1823

Jul 31, 2019

RX23W Group

37. Serial Sound Interface (SSI)

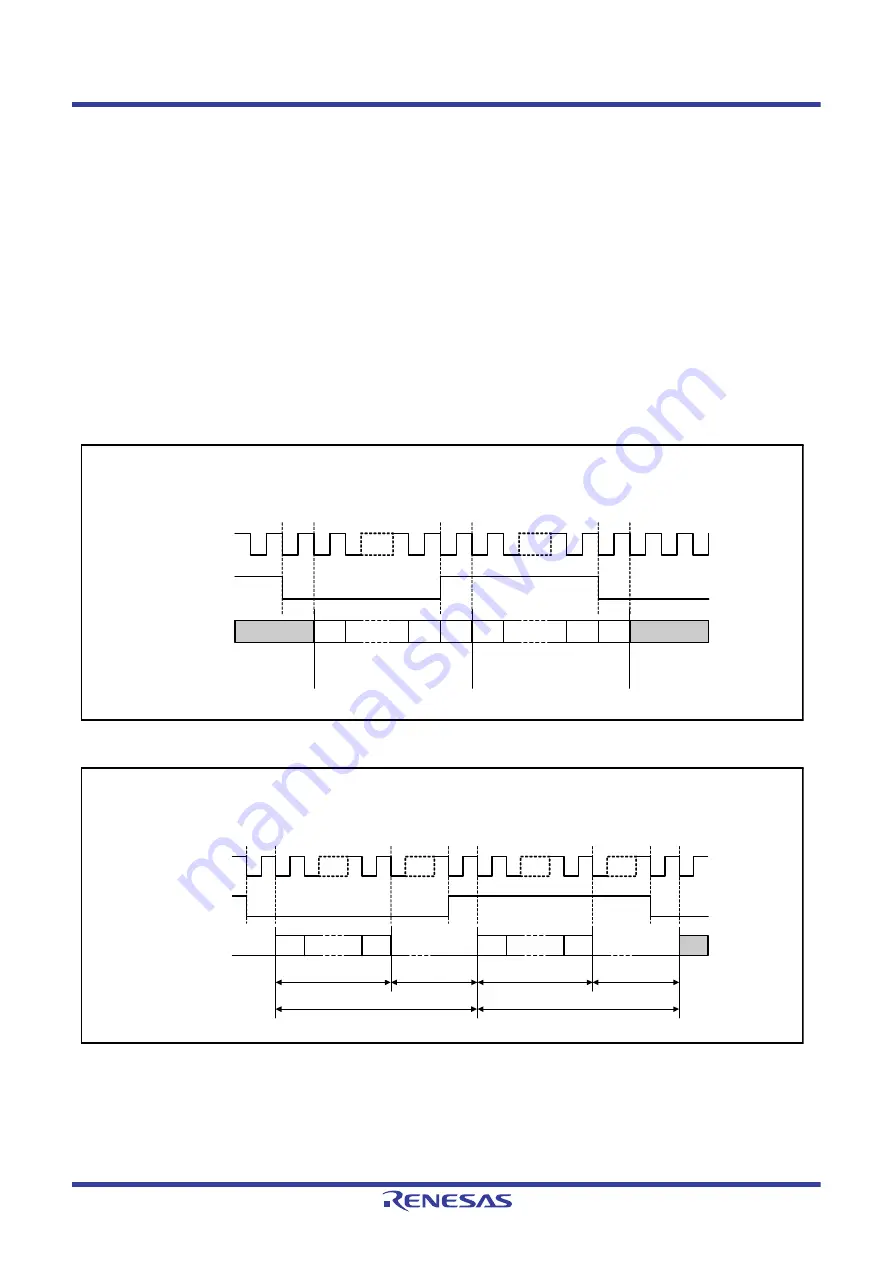

(6) Master Transceiver

This mode allows serial data transmission and reception between this module and another device. The clock and word

select signals are internally derived from the master clock. The format of these signals is defined in the configuration

fields of this module.

(7) Operating Settings Related to Word Length

All bits related to the SSICR register's word length are valid in non-compressed modes. There are many configurations

this module supports, but some of the combinations are shown below for the I

2

S compatible format, MSB-first and left-

justified format, and MSB-first and right-justified format.

In this section SSITXD0 and SSIRXD0 are referred to SSIDATA.

I

2

S Compatible Format

show the I

2

S compatible format both without and with padding.

Padding occurs when the data word length is smaller than the system word length.

Figure 37.2

I

2

S Compatible Format (without Padding)

Figure 37.3

I

2

S Compatible Format (with Padding)

Prev. sample

Next sample

SSICR.SCKP bit = 0, SSICR.SWSP bit = 0, SSICR.DEL bit = 0, SSICR.CHNL[1:0] bits = 00b

System word length = data word length

SSISCK

SSIWS

SSIDATA

System word 1 =

data word 1

System word 2 =

data word 2

MSB

LSB+1

LSB MSB

LSB+1

LSB

Next

SSICR.SCKP bit = 0, SSICR.SWSP bit = 0, SSICR.DEL bit = 0, SSICR.CHNL[1:0] bits = 00b, SSICR.SPDP bit = 0,

SSICR.SDTA bit = 0

System word length > data word length

SSISCK

SSIWS

SSIDATA

System word 1

MSB

LSB

MSB

LSB

Data word 1

System word 2

Padding

Data word 2

Padding