R01UH0823EJ0100 Rev.1.00

Page 1443 of 1823

Jul 31, 2019

RX23W Group

40. SD Host Interface (SDHIa)

—

This flag becomes 1 under the following condition:

During a multi-block read sequence triggered by CMD53 being issued, the SDIOMD.RWREQ bit is set to 1 while

the last block is being transferred.

—

This flag becomes 0 under the following condition:

The flag is set to 0.

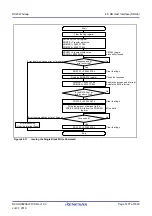

40.2.18 SDIO Interrupt Mask Register (SDIOIMSK)

The SDIOIMSK register enables and disables the interrupt requests from the status flags in the SDIOSTS register. Refer

to

for details on the relationship between the status flags and the requested interrupt

source.

SDIOIMSK

Address(es): SDHI.SDIOIMSK 0008 AC70h

b31

b30

b29

b28

b27

b26

b25

b24

—

—

—

—

—

—

—

—

Value after reset:

0

0

0

0

0

0

0

0

b23

b22

b21

b20

b19

b18

b17

b16

—

—

—

—

—

—

—

—

Value after reset:

0

0

0

0

0

0

0

0

b15

b14

b13

b12

b11

b10

b9

b8

EXWTM

EXPUB52M

—

—

—

—

—

—

Value after reset:

1

1

0

0

0

0

0

0

b7

b6

b5

b4

b3

b2

b1

b0

—

—

—

—

—

—

—

IOIRQM

Value after reset:

0

0

0

0

0

1

1

1

Bit

Symbol

Bit Name

Description

R/W

b0

IOIRQ Interrupt Mask Control

0: IOIRQ interrupt not masked

1: IOIRQ interrupt masked

R/W

b2, b1

—

Reserved

These bits are 1 when read. Set them to 1 when writing.

R/W

b13 to b3

—

Reserved

These bits are 0 when read and cannot be modified.

R

b14

EXPUB52 Interrupt Request Mask

Control

0: EXPUB52 interrupt request not masked

1: EXPUB52 interrupt request masked

R/W

b15

EXWT Interrupt Request Mask

Control

0: EXWT interrupt request not masked

1: EXWT interrupt request masked

R/W

b31 to b16

—

Reserved

These bits are 0 when read and cannot be modified.

R