R01UH0823EJ0100 Rev.1.00

Page 1645 of 1823

Jul 31, 2019

RX23W Group

47. Comparator B (CMPBa)

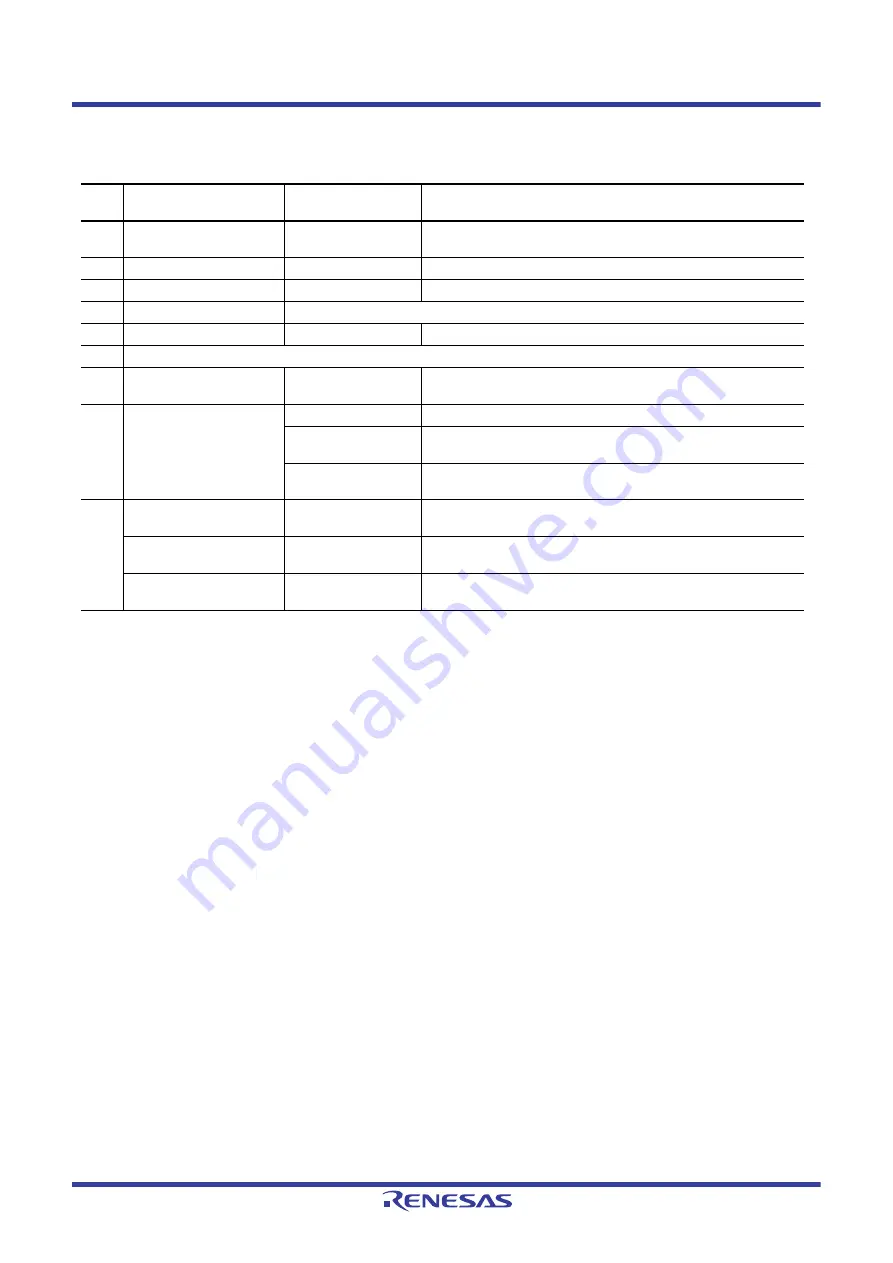

Table 47.4

Procedure for Setting Registers Associated with Comparator B When Window Function is Enabled

(n = 2, 3)

Step

No.

Register

Bit

Setting

1

PijPFS of the port to which

the CMPBn pin is assigned

ASEL

1

2

CPB1MD

CPBSPDMD

0 (always specify high-speed mode)

3

CPB1CNT1

CPBnINI

Powered on: 1

4

CPB1F

Select whether to enable or disable the filter and select the sampling clock.

5

CPB1CNT2

CPBnWCP

1 (operation enabled)

6

Waiting for the comparator stabilization time (min. 100 μs)

7

CPB1OCR

CPBnOP, CPBnOE

Set the CMPOBn output (select the polarity and set output enabled or

disabled).

8

CPB1INT

CPBnINTEN

When using an interrupt: 1 (interrupt enabled)

CPBnINTEG

When using an interrupt or the ELC: Select the input edge (1 = both

edges or 0 = single edge).

CPBnINTPL

When using an interrupt or the ELC: For CPBnINTEG = 0 (single edge

selected), select the input polarity (1 = rising edge or 0 = falling edge).

9

IPR104 (comparator B2),

IPR105 (comparator B3)

IPR[3:0]

When using an interrupt: Select the interrupt priority level.

IR104 (comparator B2),

IR105 (comparator B3)

IR

When using an interrupt: 0 (no interrupt requested: initialization)

IER07

IEN0 (comparator B2),

IEN1 (comparator B3)

When using an interrupt: 1 (interrupt enabled)