R01UH0823EJ0100 Rev.1.00

Page 1662 of 1823

Jul 31, 2019

RX23W Group

50. Flash Memory (FLASH)

50.4

Register Descriptions

50.4.1

E2 DataFlash Control Register (DFLCTL)

Note 1. Start-up area information program and access window information program

The DFLCTL register is used to enable or disable access (read, program, and erase) to the E2 DataFlash and access

(start-up area information program, and access window information program) to the extra area in P/E mode.

When reading, programming, and erasing the E2 DataFlash, set the DFLCTL.DFLEN bit to 1 and wait for the E2

DataFlash STOP recovery time (tDSTOP) to elapse before reading the E2 DataFlash and entering E2 DataFlash P/E

mode. Do not read the E2 DataFlash or enter E2 DataFlash P/E mode until tDSTOP has elapsed.

Refer to

section 50.7.1, Sequencer Modes

for details on E2 DataFlash P/E mode. Refer to

for E2 DataFlash STOP recovery time (tDSTOP).

Address(es): FLASH.DFLCTL 007F C090h

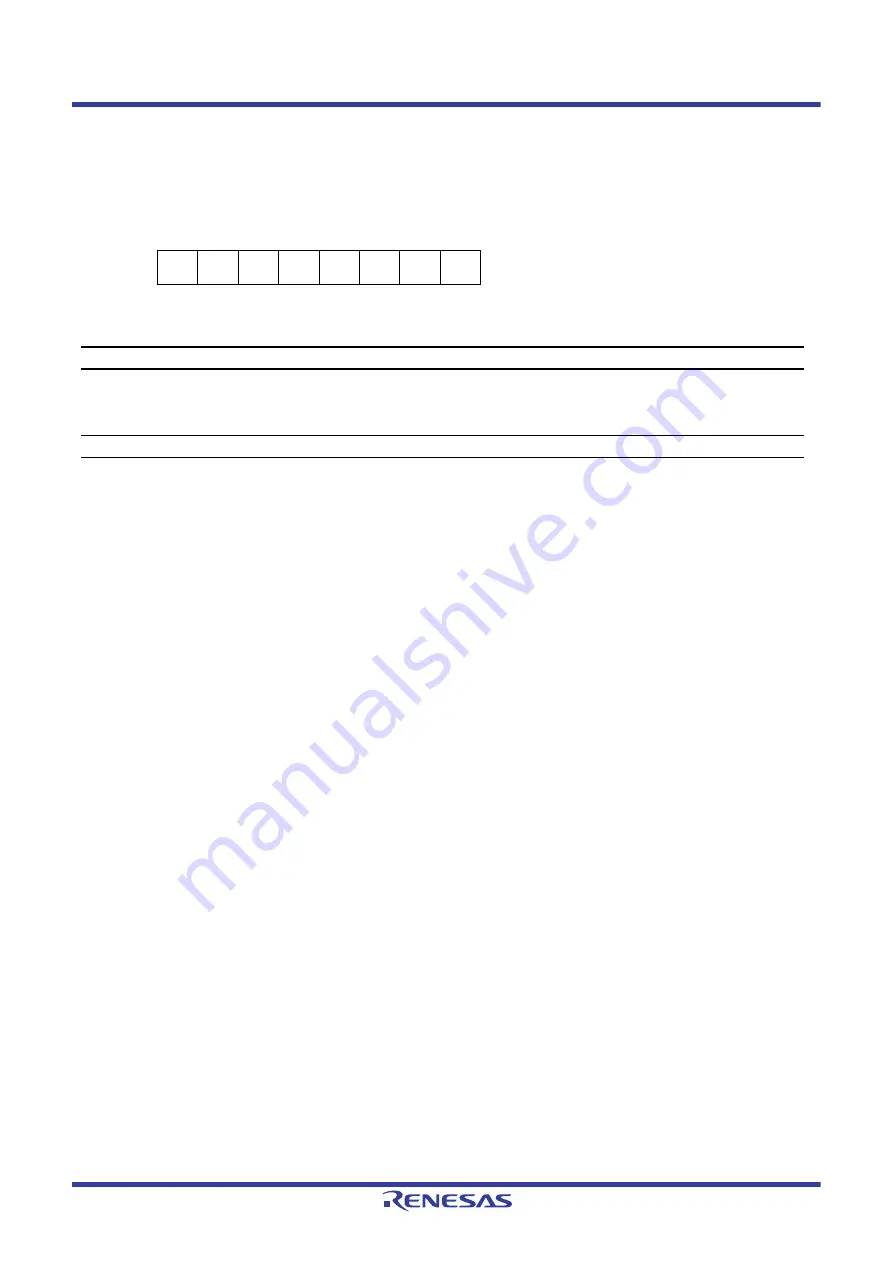

b7

b6

b5

b4

b3

b2

b1

b0

—

—

—

—

—

—

—

DFLEN

Value after reset:

0

0

0

0

0

0

0

0

Bit

Symbol

Bit Name

Description

R/W

b0

E2 DataFlash Access

Enable

0: Access to E2 DataFlash and access to the extra area in P/E mode*

disabled

1: Access to E2 DataFlash and access to the extra area in P/E mode*

enabled

R/W

b7 to b1

—

Reserved

These bits are read as 0. The write value should be 0.

R/W