R01UH0823EJ0100 Rev.1.00

Page 309 of 1823

Jul 31, 2019

RX23W Group

16. Buses

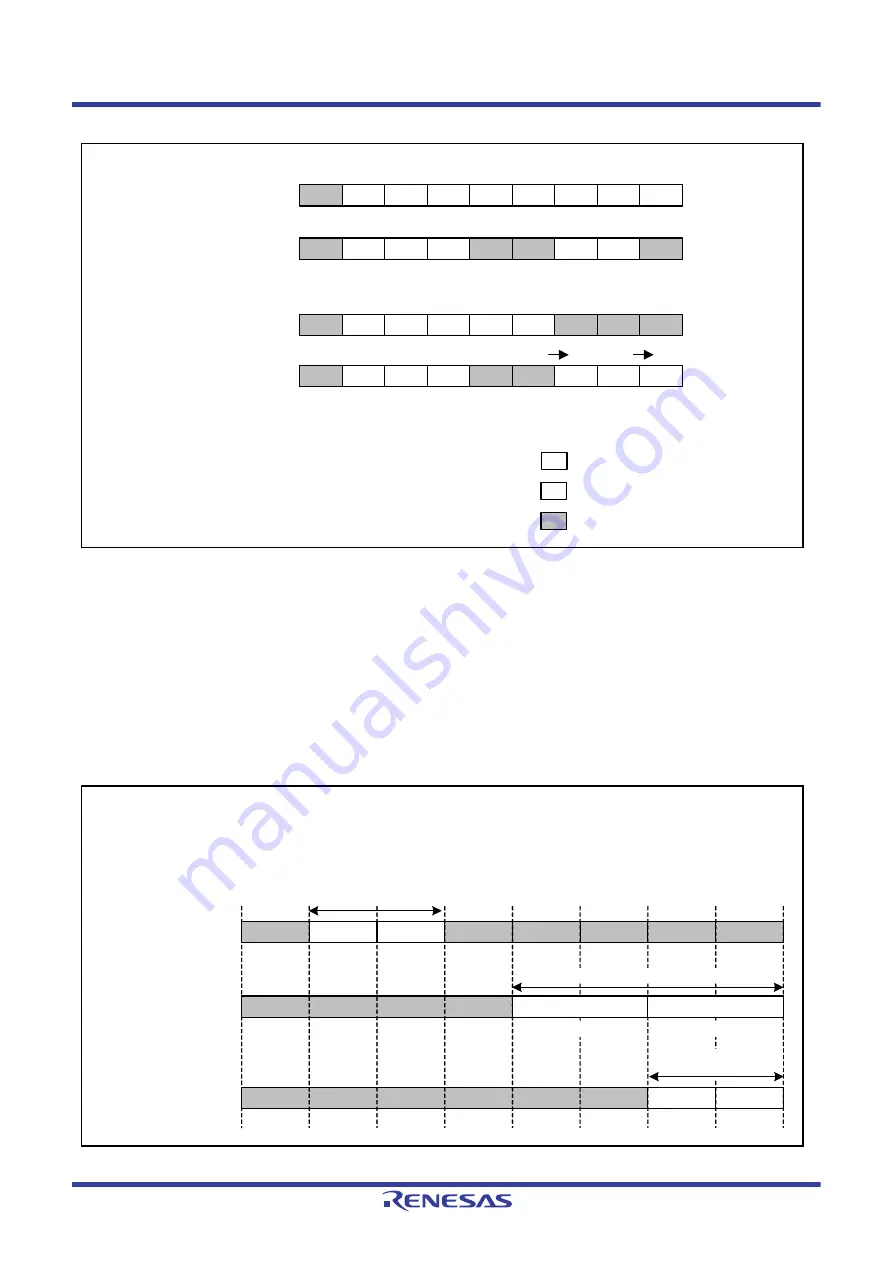

Figure 16.2

Priority Order between Internal Peripheral Bus Accesses

16.2.5

Write Buffer Function (Internal Peripheral Bus)

The internal peripheral bus has the write buffer function, which allows the next round of bus access to start, before the

current write access is completed, in write access. However, if the following round of bus access is from the same bus

master but to the different internal peripheral bus, it is suspended until the bus operations already in progress are

completed. When read access to the internal memory is scheduled after the write access to the internal peripheral bus

from the CPU, the following round of bus access can be started before the current bus operation is completed and thus

the order of accesses may be changed (Refer to

).

Figure 16.3

Write Buffer Function

Internal main bus 2

(R11)

R12

R24

R25

R21

Internal main bus 1

(R11)

R22

R23

(R11)

R11

Internal main bus 2

(R11)

R13

R25

R23

R24

R21

Internal main bus 1

R11

(R22)

R22

(R12)

R12

(R13) (R13)

R13

Request issued; not accepted

Request issued; accepted

No request issued

Priority order fixed:

Priority order toggled:

(1)

(2)

(*)

*

(1), (2) : The priority order does not change because the priority of the accepted request is low.

Internal peripheral bus 2

Internal peripheral bus 1

Memory bus 1

RAM

RAM

Write access to peripheral bus 1

Access by the CPU:

(1) Peripheral bus 1 (W)

(2) Peripheral bus 1 (W)

(3) Peripheral bus 2 (W)

(4) Peripheral bus 2 (W)

(5) RAM (R)

(6) RAM (R)

Number of access cycles: 1 cycle (peripheral bus 1), 2 cycles (peripheral bus 2)

(1)

(2)

(5)

(6)

(3)

(4)

Write access to peripheral bus 2

Read access to

RAM

Peripheral bus 2

Peripheral bus 2

Peripheral

bus 1

Peripheral

bus 1