R01UH0823EJ0100 Rev.1.00

Page 725 of 1823

Jul 31, 2019

RX23W Group

25. 16-Bit Timer Pulse Unit (TPUa)

25.9.17

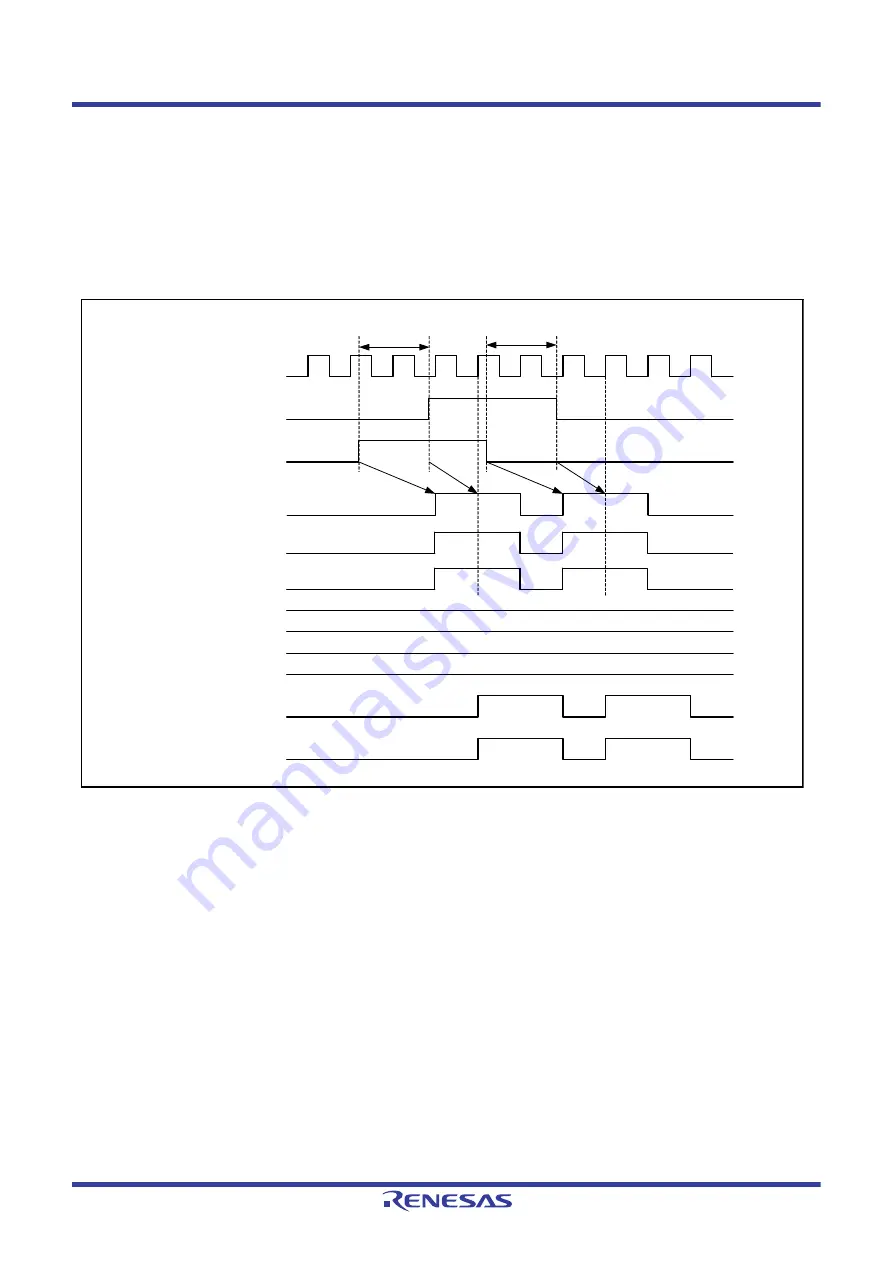

Continuous Output of Underflow Pulse Interrupt Signal

If two external clock signals' same direction edges to be phase counted are generated within two PCLK cycles in phase

counting mode 1, with TGR being 0000h, and compare match set as the counter clear source, the TCNT remains 0000h

and is not updated, and a compare-match pulse interrupt signal and an underflow interrupt signal are output continuously

to form a flat signal level.

When a pulse interrupt signal is used, the interrupt controller cannot detect the second and subsequent interrupts.

shows an operation timing when the underflow pulse interrupt signal is output continuously.

Figure 25.55

Continuous Output of Underflow Pulse Interrupt Signal

PCLK

Less than 2 PCLK cycles Less than 2 PCLK cycles

TCLKA

TCLKB

Count-down signal

Compare match

(counter clear) signal

Underflow signal

0000h

0000h

TCNT

TGRA

Compare-match pulse

interrupt signal

Underflow pulse

interrupt signal