R01UH0823EJ0100 Rev.1.00

Page 989 of 1823

Jul 31, 2019

RX23W Group

33. Serial Communications Interface (SCIg, SCIh)

lists examples of N settings in BRR in normal asynchronous mode.

lists the maximum bit rate

settable for each operating frequency. Examples of BRR (N) settings in clock synchronous mode and simple SPI mode

are listed in

. Examples of BRR (N) settings in smart card interface mode are listed in

Examples of BRR (N) settings in simple I

2

. In smart card interface mode, the number of

base clock cycles S in a 1-bit data transfer time can be selected. For details, refer to

Sampling Timing and Reception Margin

list the maximum bit rates with external

clock input.

When either the SEMR.ABCS or BGDM bit is set to 1 in asynchronous mode, the bit rate becomes twice that listed in

. When both of those bits are set to 1, the bit rate becomes four times the listed value.

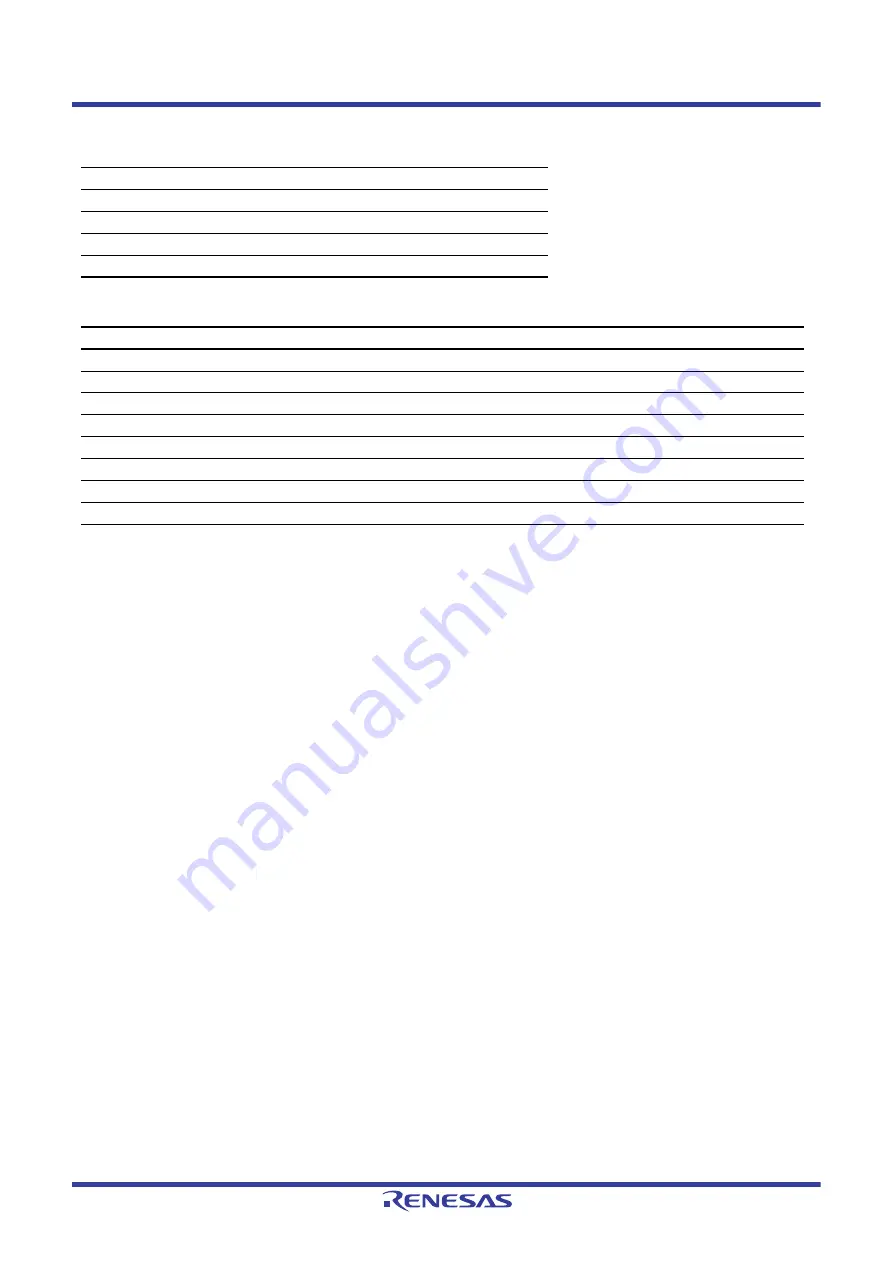

Table 33.12

Clock Source Settings

SMR.CKS[1:0] Bit Setting

Clock Source

n

0 0

PCLK

0

0 1

PCLK/4

1

1 0

PCLK/16

2

1 1

PCLK/64

3

Table 33.13

Base Clock Settings in Smart Card Interface Mode

SCMR.BCP2 Bit Setting

SMR.BCP[1:0] Bit Setting

Base Clock Cycles for 1-bit Period

S

0

0 0

93 clock cycles

93

0

0 1

128 clock cycles

128

0

1 0

186 clock cycles

186

0

1 1

512 clock cycles

512

1

0 0

32 clock cycles

32

1

0 1

64 clock cycles

64

1

1 0

372 clock cycles

372

1

1 1

256 clock cycles

256