R01UH0823EJ0100 Rev.1.00

Page 1491 of 1823

Jul 31, 2019

RX23W Group

43. Capacitive Touch Sensing Unit (CTSU)

43.1

Overview

lists the specifications of the CTSU, and

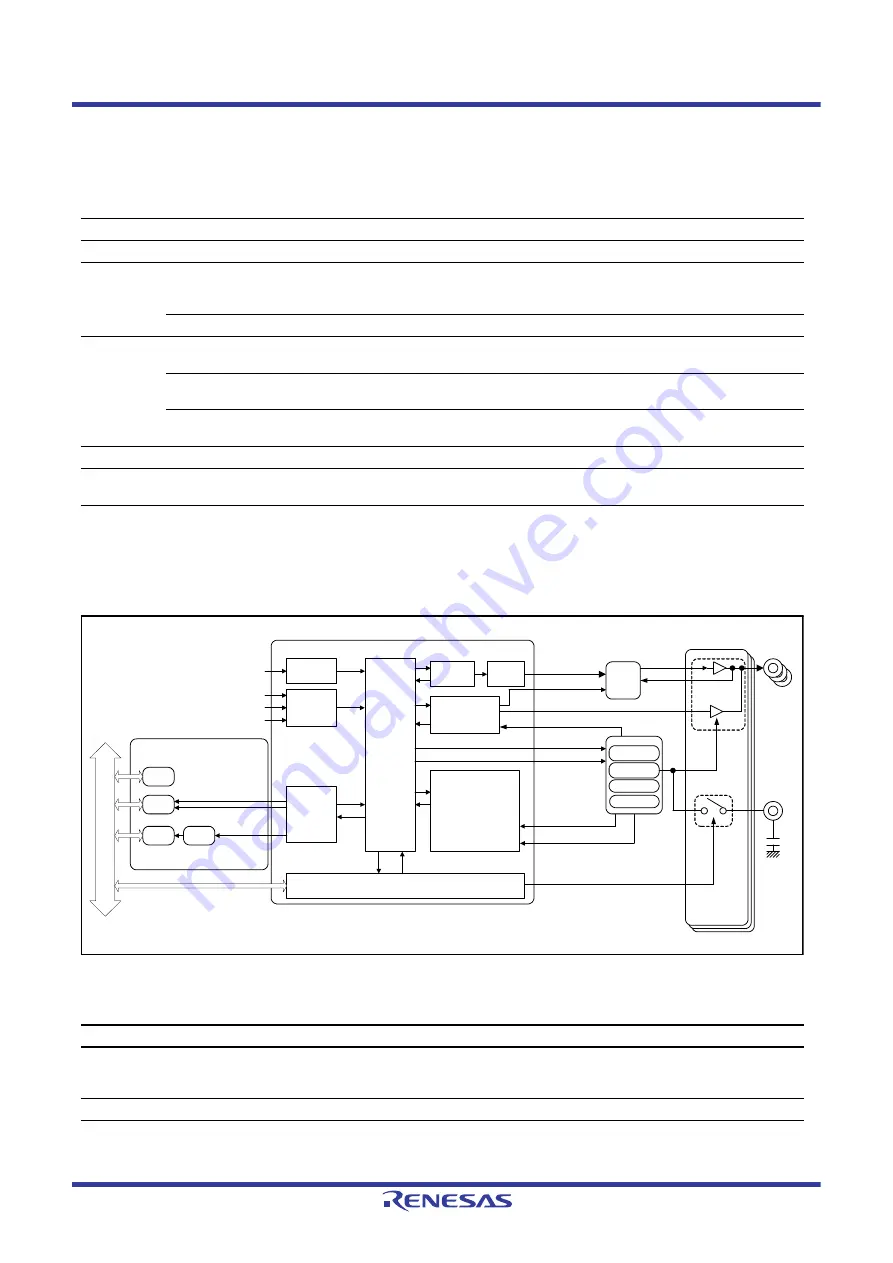

shows a block diagram of the CTSU.

As shown in

, the CTSU consists of the status control block, trigger control block, clock control block,

channel control block, port control block, sensor drive pulse generator, measurement block, interrupt block, and control

registers.

Figure 43.3

CTSU Block Diagram (m = 2, 3, 4, 7, 8, 12, 13, 22, 23, 27, 30, 35)

Table 43.1

CTSU Specifications

Item

Description

Operating clock

PCLK, PCLK/2, or PCLK/4

Pins

TS2, TS3, TS4, TS7, TS8, TS12,

TS13, TS22, TS23, TS27, TS30,

TS35

Electrostatic capacitance measurement pins (12 channels)

TSCAP

LPF (low-pass filter) connection pin

Measurement

modes

Self-capacitance single scan

mode

Electrostatic capacitance on a channel is measured by the self-capacitance

method.

Self-capacitance multi-scan mode Electrostatic capacitance on multiple channels is measured successively by the

self-capacitance method.

Mutual capacitance full scan

mode

Electrostatic capacitance on multiple channels is measured successively by

mutual capacitance.

Noise prevention

Synchronous noise prevention, high-pass noise prevention

Measurement start conditions

Software trigger

External trigger (event input from the event link controller (ELC))

Table 43.2

CTSU Pin Configuration

Pin Name

I/O

Function

TS2, TS3, TS4, TS7, TS8, TS12,

TS13, TS22, TS23, TS27, TS30,

TS35

I/O

Electrostatic capacitive measurement pins (touch pins)

TSCAP

—

LPF connection pin

System control block

Trigger

control block

Status

control

Capacitive touch sensing unit (CTSU)

Channel

control block

PCLK

PCLK/2

PCLK/4

Event input from event link

controller (ELC)

Port

control

Measurement block

(counter measurement)

• CTSUSC counter

• CTSURC counter

Clock

control

block

Sensor drive

pulse generator

Interrupt

block

Port control

Sensor drive pulse

Operation enable

Control registers

Offset control

Sensor ICO clock

Reference ICO clock

Port

control

block

Power

supply

DTC

CTSURD interrupt request

D

at

a

bus

Memory

CTSUWR interrupt request

CPU

ICU

CTSUFN

interrupt request

Diffusion clock

Count

source

H/M

Sensor ICO

Reference ICO

Power supply

control

Diffusion clock

Touch I/O

I/O block

TSCAP

LPF

TSCAP I/O

TSm

ICO: Current-Controlled Oscillator