R01UH0823EJ0100 Rev.1.00

Page 1791 of 1823

Jul 31, 2019

RX23W Group

51. Electrical Characteristics

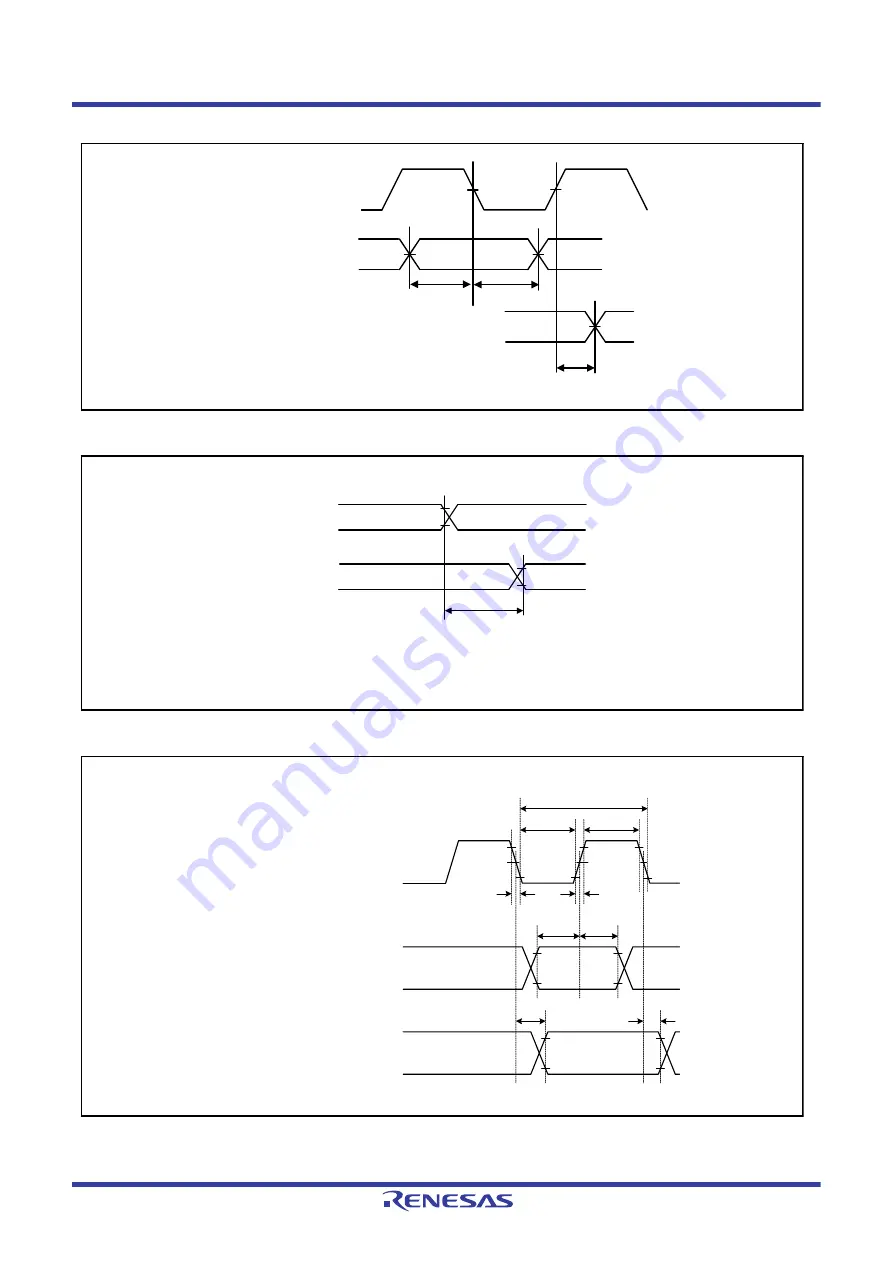

Figure 51.52

SSI Transmission/Reception Timing (SSICR.SCKP=1)

Figure 51.53

SSIDATA Output Delay After SSIWSn Changing Edge

Figure 51.54

SD Host Interface Input/Output Signal Timing

t

SR

t

HTR

t

DTR

SSISCKn

(input or output)

SSIWSn, SSIDATAn,

SSIRXDn (input)

SSIWSn, SSIDATAn,

SSITXDn (output)

t

DTRW

SSIWSn (input)

SSIDATAn (output)

Note. Timing to output the MSB bit during slave transmission from SSIWSn

when DEL = 1 and SDTA = 0 or DEL = 1, SDTA = 1, and SWL[2:0] = DWL[2:0]

SDHI_CLK output

SDHI_CMD, SDHI_D3 to SDHI_D0 input

SDHI_CMD, SDHI_D3 to SDHI_D0 output

t

WL(SD)

t

WH(SD)

t

PP(SD)

t

ISU(SD)

t

IH(SD)

t

TLH(SD)

t

THL(SD)

t

ODLY(SD)

t

ODLY(SD)

V

IH

V

IL

V

IL

V

IL

V

IH

V

IH

50% V

CC

50% V

CC