R01UH0823EJ0100 Rev.1.00

Page 578 of 1823

Jul 31, 2019

RX23W Group

23. Multi-Function Timer Pulse Unit 2 (MTU2a)

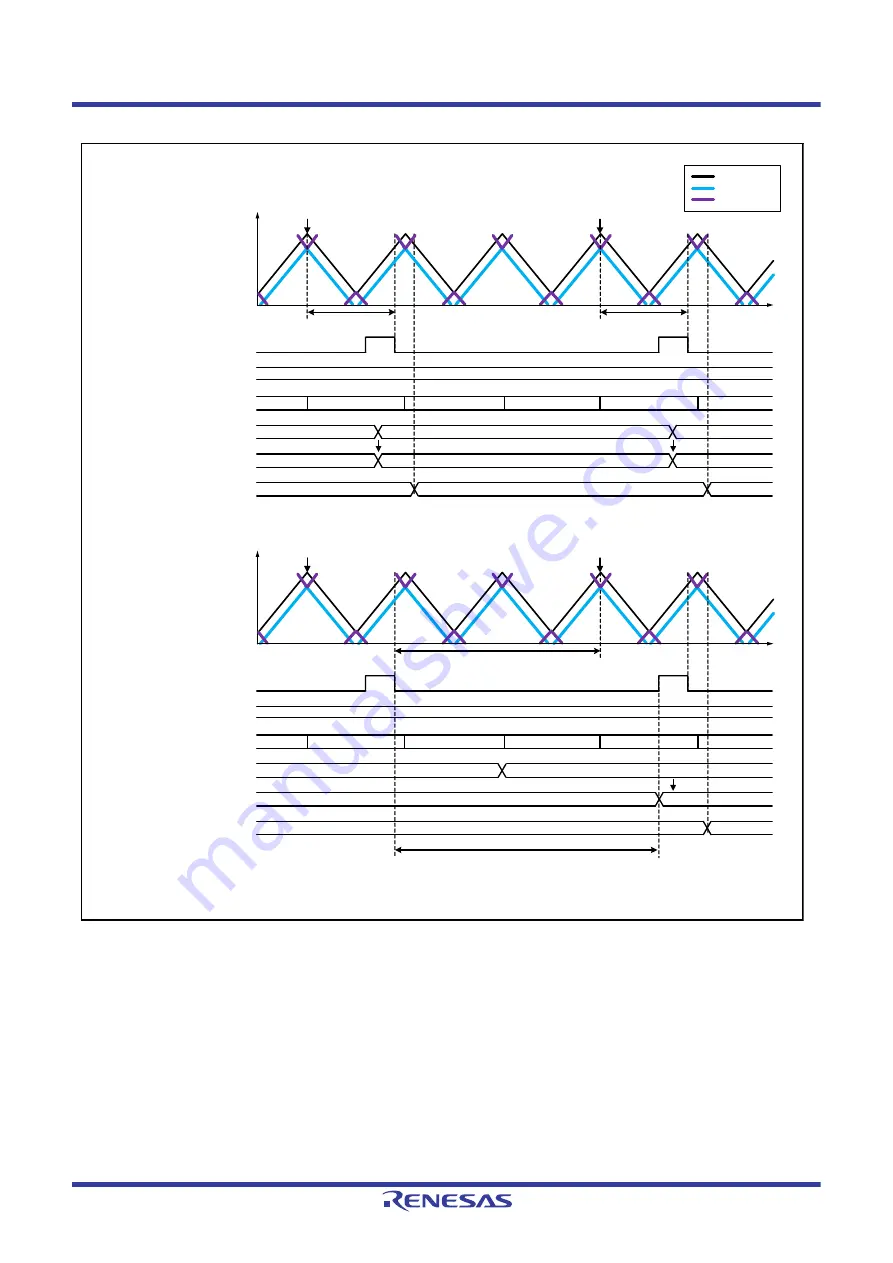

Figure 23.71

Example of Operation When Buffer Transfer is Linked with Interrupt Skipping

(TBTER.BTE[1:0] = 10b)

MTU3.TCNT

MTU4.TCNT

TCNTSA

(1) When the buffer register is modified within one carrier cycle after a TGIA3 interrupt

Buffer transfer-enabled period

TITCR1A.T3ACOR[2:0] bits

TITCNT1A.T3ACNT[2:0] bits

Buffer register

Temporary register

Compare register

TGIA3 generated

MTU3.

TCNT

MTU4.

TCNT

Timing for modifying

the buffer register

Timing for modifying

the buffer register

Data

Data

Data

Data1

Data1

Data1

Data2

Data2

Data2

2

2

1

1

0

0

TGIA3 generated

(2) When the buffer register is modified after one carrier cycle has elapsed after a TGIA3 interrupt

Buffer transfer-enabled period

TITCR1A.T3ACOR[2:0] bits

TITCNT1A.T3ACNT[2:0] bits

Buffer register

Temporary register

Compare register

TGIA3 generated

MTU3.

TCNT

MTU4.

TCNT

Timing for modifying the buffer register

Data

Data

Data

Data1

Data1

Data1

2

2

1

1

0

0

TGIA3 generated

Note:

Buffer transfer at the crest is selected.

The skipping count is set to two.

The TITCR1A.T3AEN bit is set to 1.

Buffer transfer disabled