A32

A10

10

6

4

1

5

7

12

2

8

11

3

9

A2

A1

C3

A4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

A3

C2

C4

C32

A12

C10

C1

C12

1

2

1

22

20

2

23

21

24

25

3

4

5

6

7

8

9

10

19

18

17

16

15

13

12

11

28

14

27

26

1

2

5

6

7

8

9

10

11

12

13

14

15

16

30

29

21

22

23

24

25

26

27

28

10

11

12

13

14

15

16

17

9

31

39

38

37

36

35

34

33

32

1

2

3

4

5

6

7

8

19

18

TEST

NORM

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

J3

R7

R8

R6

CR12

CR16

CR15

CR8

CR14

CR9

CR13

CR10

CR11

U6

C2

C27

C26

Y2

U7

TP8

C12

J6

J5

C29

U3

C1

C3

R10

R9

R11

U5

TP7

C4

+5V

+5V

+5V

+5V

RELAY_RET

+5V

+5V

+5V

+5V

+5V

+5V

COMINT

RXD

HC2

RST_LOG

HC1

HC4

ST_TEST

DISP_SLT

HC3

DOWN

P1.6

UP

AD7

AD7

AD7

A13

A13

AD6

AD6

AD6

ALE

P1.3

P1.2

A15

A15

GND

P1.5

ROMS

ROMS

A15

A15

P1.1

A0

A0

P1.4

A12

A12

A12

CHASSIS

RD

RD

TXD

AD4

AD4

AD4

AD1

AD1

AD1

AD0

AD0

AD0

WR

WR

A4

A4

A7

A7

A3

A3

A6

A6

AD2

AD2

AD2

A1

A1

A11

A11

A11

A10

A10

A10

A8

A8

A8

AD3

AD3

AD3

A9

A9

A9

A14

A14

AD5

AD5

AD5

A5

A5

A2

A2

SLAVE COMMS

HEAD SLAVE/

47.5K

47.5K

47.5K

1N914B

1N914B

1N914B

1N914B

1N914B

1N914B

1N914B

1N914B

1N914B

CE

A15

OE

GND

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

D0

D1

D2

D3

D4

D5

D6

D7

VCC

27C512

.01UF

33pF

33pF

12MHZ

WR

A11

A14

A13

A12

OE

CE

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

O7

O6

O5

O4

O3

O2

O1

O0

GND

VCC

DS1644

.1uF

120pF

VBAT

VOUT

BAT

LOW

OSCIN

OSCSEL

PFI

PFO

WDI

CEOUT

CEIN

WDO

RES

RES

MAX691EPE

35V

47uF

.1uF

4.99K

4.99K

47.5K

P3.7

P3.6

P3.5

P3.4

P3.3

P3.2

P3.1

P3.0

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P0.7

P0.6

P0.5

P0.4

P0.3

P0.2

P0.1

P0.0

PSEN

ALE

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RESET

XTAL1

XTAL2

EA

80C32

.1uF

A0 THRU A7, A13, A14

-THRU-

SHEET 3

PUSHBUTTON INPUTS

TO SHEET 2

AD(0:7)

P1

RST

RST

RST

RST

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

SPARE

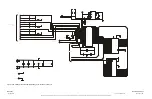

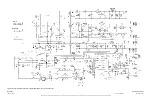

Figure 16-20. Schematic, RFL 9785 Checkback (Dwg. No. D-106529-C) Sheet 1 of 3

RFL

9785

RFL

Electronics

Inc.

July 26, 2007

16-31 (16-32 Blank)

(973) 334-3100