10/16

●

Reference data (PLL : Long Term Jitter data)

This data represents Period-Jitter at the 1000th cycle.

●

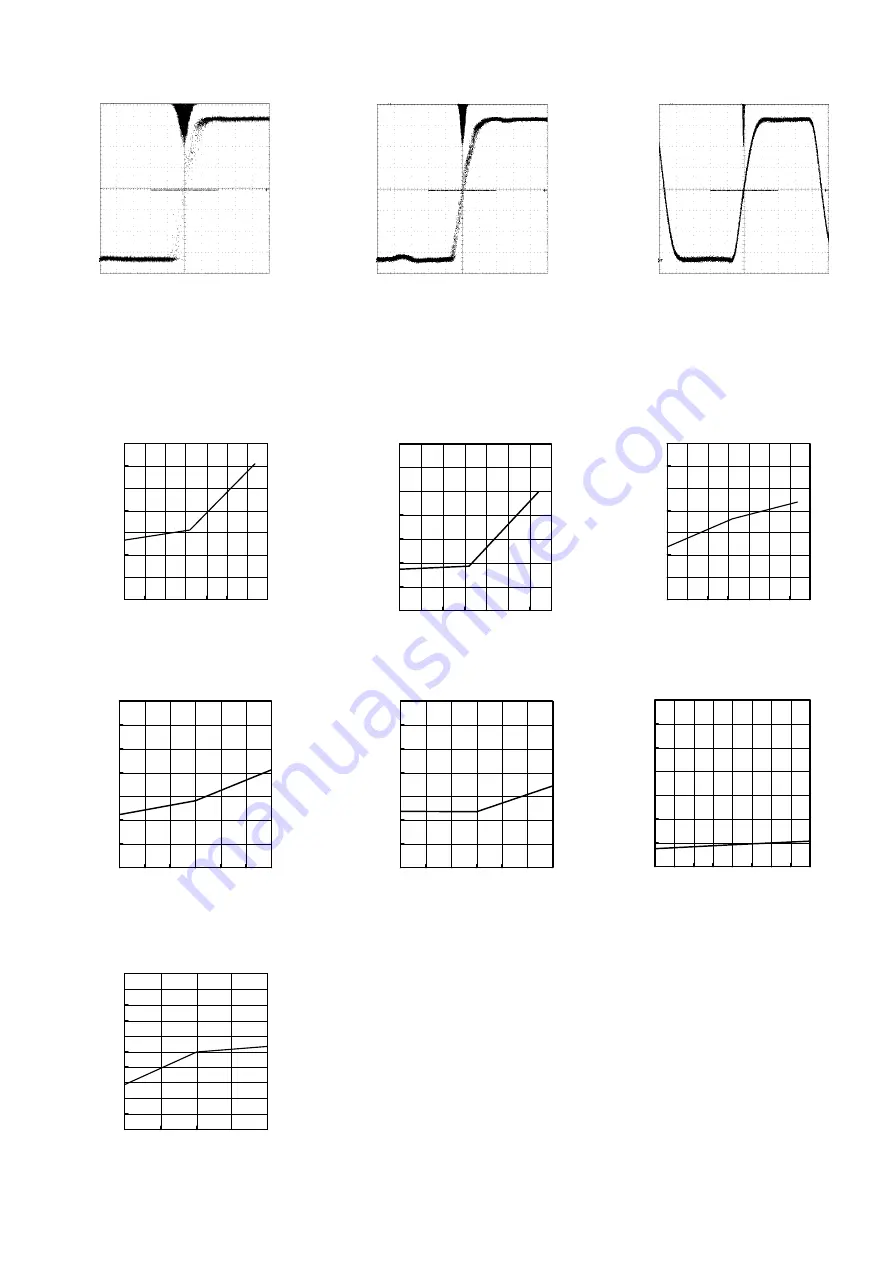

Reference data (Period-Jitter MIN-MAX

Output load CL dependence data)

This data represents the output load up to two times as high as the maximum load of each output.

Since the 27-MHz buffer is dependent on the jitter of a clock input, the output is represented by the ratio to the jitter at 50pF.

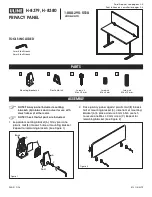

Fig.67 33.8688MHz

Long Term Jitter

Fig.68 36.864MHz

Long Term Jitter

Fig.69 54MHz

Long Term Jitter

Fig.70 33.8688MHz

CL

-

Period-Jitter MIN-MAX

Fig.71 36.864MHz

CL

-

Period-Jitter MIN-MAX

Fig.72 18.432MHz

CL

-

Period-Jitter MIN-MAX

Fig.73 24.576MHz

CL

-

Period-Jitter MIN-MAX

Fig.74 54MHz

CL

-

Period-Jitter MIN-MAX

Fig.75 27MHz VCXO

CL

-

Period-Jitter MIN-MAX

0

100

200

300

400

500

600

700

0

10 20 30 40 50 60 70

Output Load

:

CL [pF]

Period-Jitter MIN-MAX

:

P-JMIN-MAX [psec]

VDD=3.3V

0

100

200

300

400

500

600

700

0 10 20 30 40 50 60 70

Output Load

:

CL [pF]

P

erio

d-

Ji

tte

r MIN-MA

X

:

P-

JMI

N

-M

AX [

psec]

VDD=3.3V

0

100

200

300

400

500

600

700

0 10 20 30 40 50 60 70

Output Load

:

CL [pF]

P

erio

d-

Ji

tte

r MIN-MA

X

:

P-

JMI

N

-M

AX [

psec]

VDD=3.3V

0

100

200

300

400

500

600

700

0

5

10

15

20

25

30

Output Load

:

CL [pF]

Period-Jitter MIN-MAX

:

P-JMIN-MAX [psec]

VDD=3.3V

0

100

200

300

400

500

600

700

0

5

10

15

20

25

30

Output Load

:

CL [pF]

Period-Jitter MIN-MAX

:

P-JMIN-MAX [psec]

VDD=3.3V

0

100

200

300

400

500

600

700

0

1

2

3

4

5

6

7

8

Output Load

:

CL [pF]

Period-Jit

ter MI

N-MAX

:

P-JMIN-MAX [psec]

VDD=3.3V

Fig.76 27MHz BUFFER

CL

-

Period-Jitter MIN-MAX

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

1.8

2

0

25

50

75

100

Output Load

:

CL [pF]

P

erio

d-

Ji

tte

r MIN-MA

X

:

P-

JMIN-

M

AX

VDD=3.3V

0.5V

/

div

2.0nsec

/

div

0.5V

/

div

2.0nsec

/

div

0.5V

/

div

2.0nsec

/

div