12/16

●

Audio Clock Functions

1) Output phase relation

The Audio clocks (i.e., CLK768FS, CLK384FS, and CLK512FS) of the BU2365FV are designed so that these clocks will

intentionally becomes out of the phase of each output, in order to provide low jitter and noise levels. Thus, overlapped

through currents generated at the clock edges can be suppressed to provide low jitter and noise levels.

For the generation of CLK384FS (18.432 MHz), generate two-phase CLK768FS (36.864 MHz) first. The CLK768FS1 and

CLK768FS2 will get to the phase relation with one clock out of the PLL2 output (VCO

=

147.456 MHz). By dividing the

frequency in sync with the leading edge of this CLK768FS1, the CLK384FS will fall out of the phase of the CLK768FS2.

Since the frequency of CLK512FS is divided into six portions in sync with the trailing edge of the PLL2 output, the

CLK512FS will fall out of the phases of CLK768FS and CLK384FS by half cycle.

As described above, the Audio clocks of the BU2365FV fall out of the phases each other, thus providing low jitter and

noise levels.

Furthermore, the true values of phase difference (Delay rate) between CLK384FS and CLK768FS are specified as shown

below with consideration given to variations in the measurements on the tests before shipment.

MIN

TYP

MAX

True value [nsec]

17.0

20.0

23.0

2) Half-pulse clock protection [HPC]

The CLK768FS output is provided with a function used to prevent the occurrence of asynchronous droop of half cycle or less (i.e.,

half-pulse clock) while in frequency selection under the FSEL pin control.

This function is designed to set the frequency to output L fixed after the elapse of two trailing clocks of output before the selection

and to a desired frequency after the elapse of two trailing clocks of output after the selection, when switching the FSEL pin.

Specifically speaking, when the FSEL pin is set to High, the CLK768FS outputs a frequency of 36.864 MHz. With this setting, if the

FSEL pin is switched to Low, the CLK768FS will be set to L Fixed after the lapse of two trailing clocks of 36.864 MHz, and then the

CLK768FS will output a frequency of 33.8688 MHz after the lapse of two trailing clocks of 33.8688 MHz.

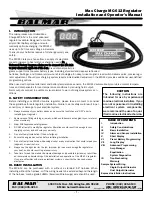

Fig.79 Audio Clock Output Circuit Configuration and Timing Chart

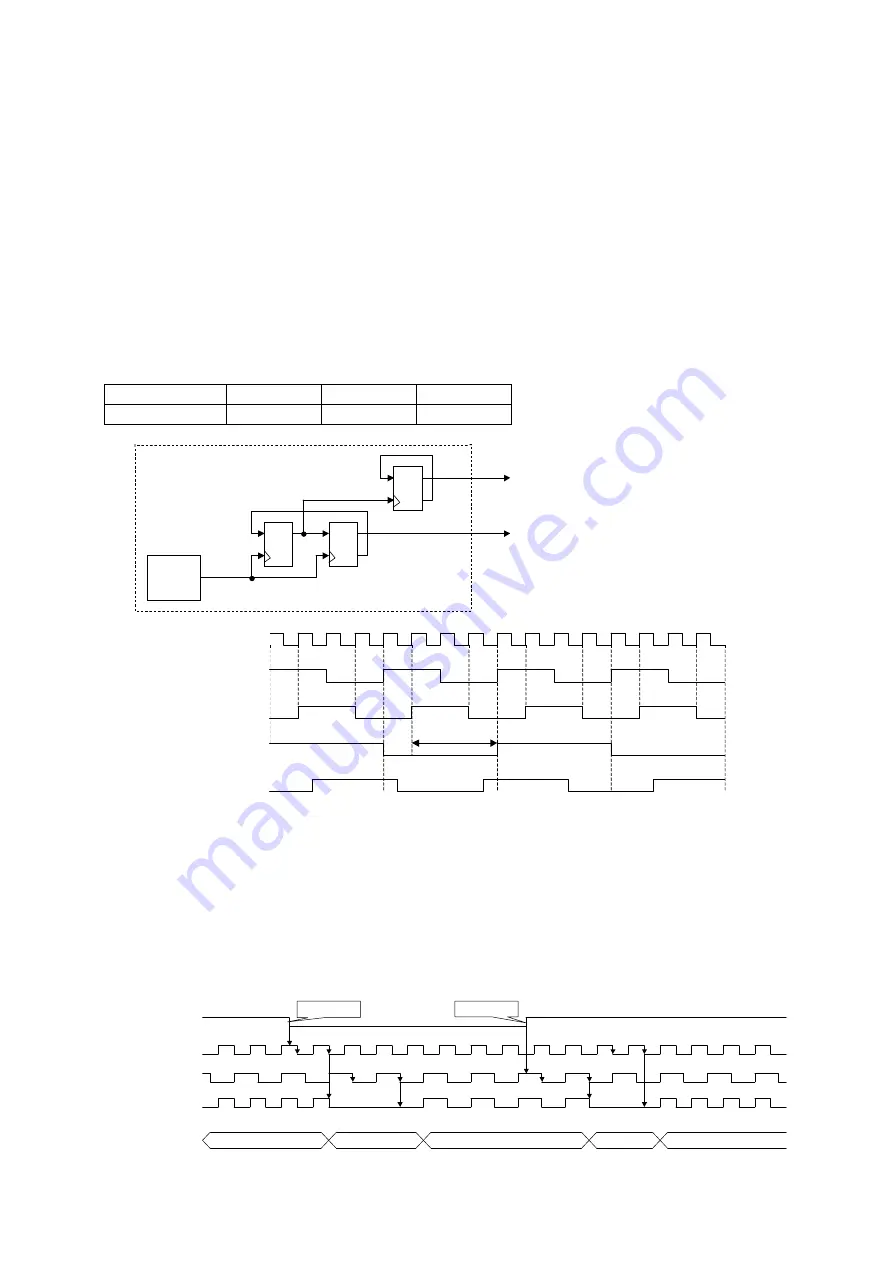

Fig.80 HPC timing chart

BU2365FV

VCO

147.456MHz

CLK768FS1

:

36.864MHz(inside)

CLK768FS2

:

36.864MHz output

CLK384FS

:

18.432MHz

D Q

QB

D Q

QB

D Q

QB

PLL2

PLL2

:

147.456MHz

CLK768FS2

:

36.864MHz

CLK768FS1

:

36.864MHz

CLK384FS

:

18.432MHz

Delay

CLK512FS

:

24.576MHz

36.864MHz output

output:L

33.8688MHz output

Output:L

36.864Hz output

FSEL

36.864MHz

33.8688MHz

CLK768FS output

H/L change

H/L change

①

①

①

①

②

②

②

②