30

Sep. 2012

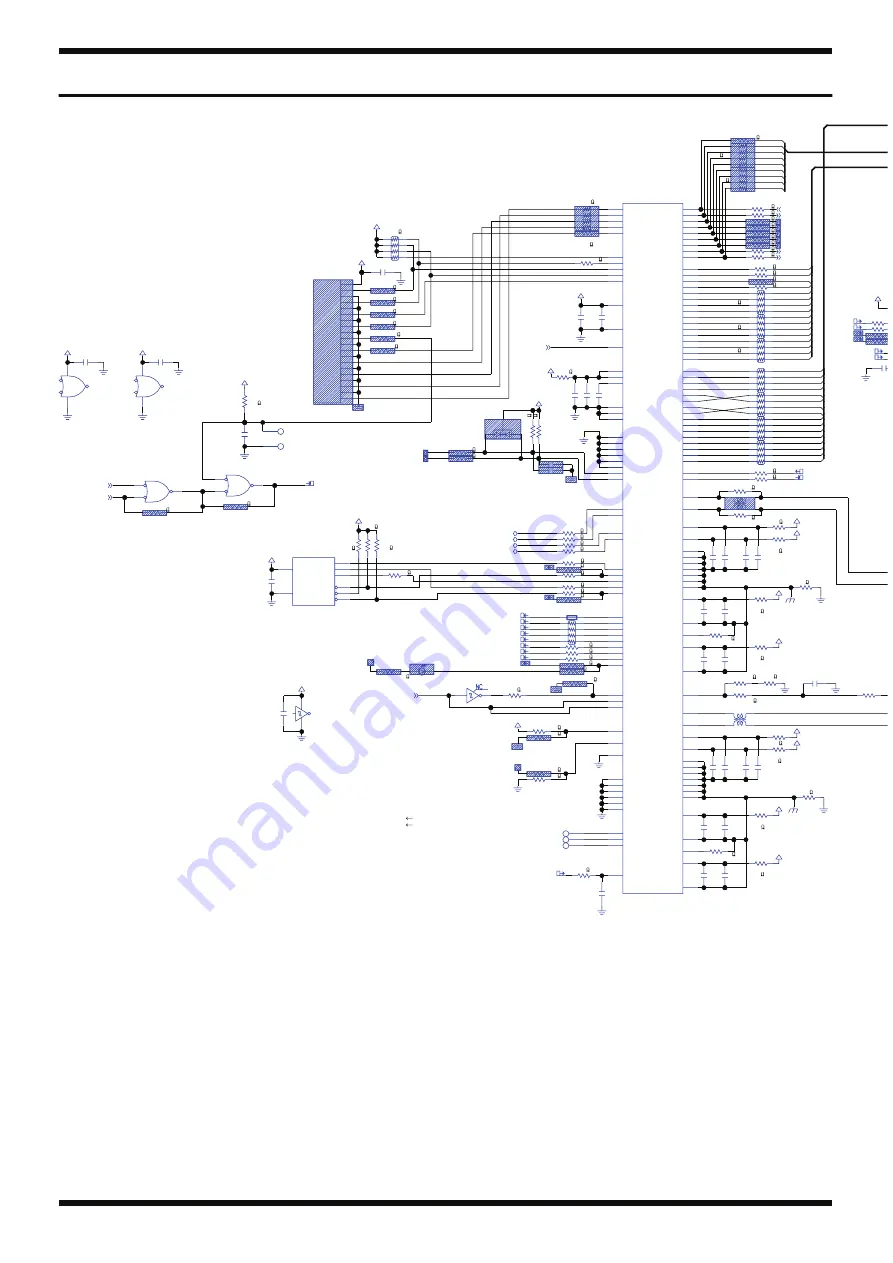

INTEGRA-7

Circuit Diagram (Main Board: 4/5)

fig.d-main4.eps@L

MD(3)

H_AGND

SFI_DO

MCKE

MA(9)

MA(5)

DGND

TRCD1

TRCD1

MDQM0

MA(10)

TMS_SWDIO_ESC2

D+3.3V

D_AGND

TRCD3

TRCD3

MA(0)

DGND

MD(15)

MA(2)

DGND

MA(14)

TDO_SWV_ESC2

DGND

MD(0)

MDQM1

MD(2)

MA(11)

XTRST_ESC2

MA(1)

DGND

XMWE

MD(6)

TRCD2

TRCD2

MA(3)

DGND

XSD_PWR

MD(5)

TCK_SWCK_ESC2

TRCCKO

TRCCKO

MD(13)

MD(7)

MD(12)

MA(15:0

MCKO

DGND

MA(4)

MA(12)

TDI_ESC2

D+3.3V

MD(4)

XMWR_CAS

DGND

MCKE

DGND

DGND

MA(8)

MD(14)

DGND

MD(1)

MA(7)

MA(15)

MD(11)

XMSDRCS

MCKO

MA(6)

TRCD0

TRCD0

EUVBON

EUOVCD

D+3.3V

CP+1.2V

D+3.3V

CP+1.2V

DGND

D+3.3V

CP+1.2V

D+3.3V

CP+1.2V

D+3.3V

SDA0

SCL0

SDA1

SCL1

CP+1.2V

D+3.3V

DGND

D+3.3V

D+3.3V

ESC2_TXD4

ESC2_RXD4

ESC2_RXD5

ESC2_TXD5

LCD_CS

LCD_RST

LCD_CD

DAC_RST

ESC2_AD1

D+3.3V

ESC2_AD0

DGND

DGND

DGND

D+3.3V

SFI_DIN

SFI-CLK

SFI_XCS0

D+3.3V

SFI_HOLD

D+3.3V

DGND

D+3.3V

DGND

XRST

STOE_RST

XSRST

DGND

D+3.3V

DGND

XRESET_ESC2

XRESET_ESC2

DGND

D+3.3V

DGND

D+3.3V

DGND

ESC2_UPD

MA(13)

MA(16)

MA(17)

MA(18)

MA(19)

MA(20)

MA(21)

MA(22)

MA(23)

MA(24)

XMRD_RAS

XFLCS

DGND

MD(9)

MD(8)

MD(10)

XMWR_CAS

XMRD_RAS

XPF_RAS

XPF_CAS

XPF_RAS

XPF_CAS

CK48M

33

R237

100k

R242

10k

R186

0

R243

1uF

C222

RA120

10

UnPop

1

8

6

5

4

3

2

7

10k

R188

MX25L3206EM2I-12G

IC30

6

SCLK

5

SI/SIO0

2

SO/SIO1

1

_CS

3

_WP

7

_HOLD

4

GND

8

VCC

0.1uF

C209

10

R194

UnPop

0.1uF

C212

0

R241

1uF

C201

0.1uF

C215

0.1uF

C204

D (0.5%)

12k

R219

0

R191

UnPop

RA123

33

1

8

6

5

4

3

2

7

0

R206

0

R190

UnPop

RA121

33

1

8

6

5

4

3

2

7

33

R223

UnPop

100pF

C196

IC31

MB8AA4181(ESC2)

P18

P19

Y14

AA13

Y13

AA12

W14

V14

V16

C15

D15

A15

D14

B15

A12

A14

A16

B12

M21

M20

L21

L20

M19

M18

K19

K18

H19

N20

N21

P20

P21

R20

R21

T20

T21

U19

U20

V19

V20

T18

T19

F2

C2

B1

Y1

B2

A2

C16

C12

D16

AA18

Y19

AA19

AA14

U18

V17

W16

AA15

Y15

B10

C10

A9

A11

B7

B11

B9

C9

D9

A7

D10

B8

A8

C19

C4

B6

D5

A6

C7

A3

B4

C5

D6

B14

B16

C13

D13

C14

B13

A13

H18

E18

K21

K20

H20

J20

V21

Y16

AA17

Y20

W17

Y18

Y17

AA16

W18

F3

A4

B5

C6

A5

F21

F20

E21

E20

H21

D8

C8

AA2

AA20

Y21

A17

C11

D11

A10

C20

D20

E19

F19

G20

B19

C21

B20

A20

B21

C18

B18

A19

B3

10k

R187

100k

R231

0.1uF

C197

0.1uF

C195

33

R220

0

R192

UnPop

TC7S08FU(TE85L.F)

IC29

3

GND

5

VCC

10

R214

UnPop

0

R207

IC29

TC7S08FU(TE85L.F)

2

4

1

0

R189

UnPop

100k

R232

0.1uF

C211

0

R246

0

R238

0

R245

CN6

FTSH-110-01-L-DV-K

UnPop

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

0

R248

RA116

10k

1

8

6

5

4

3

2

7

0.1uF

C207

0

R240

100pF

C205

33

R236

33

R221

0

R244

33

R196

10

R215

0.1uF

C194

0

R239

100

R213

0

R247

0

R205

0.1uF

C210

100

R193

UnPop

0

R204

0.1uF

C208

33

R222

UnPop

D (0.5%)

12k

R218

0.1uF

C206

RA122

33

1

8

6

5

4

3

2

7

EXB28V101JX

RA118

1

8

6

5

4

3

2

7

2

C223

33

R235

33

R234

33

R233

TP21

TP22

TP23

33

R228

10uF

C220

10uF

C218

10uF

C213

10uF

C219

10uF

C221

10uF

C216

10uF

C217

10uF

C214

33

R224

UnPop

33

R225

UnPop

33

R226

UnPop

33

R227

DAN202U T106(PB FREE)

D3

UnPop

3

2

1

0.1uF

C198

UnPop

0

R198

UnPop

0

R199

UnPop

0.1uF

C199

UnPop

10k

R202

10k

R201

0.1uF

C203

0.1uF

C202

10uF

C200

0

R203

33

R211

33

R210

33

R209

33

R208

10k

R195

SML-310LTT86

LED2

UnPop

1

2

680

R197

UnPop

0

R229

0

R230

ACM2012-900-2P-T002

L19

UnPop

1

2

3

4

ACM2012-900-2P-T002

L20

1

2

3

4

IC38

TC7S08FU(TE85L.F)

2

4

1

TC7S08FU(TE85L.F)

IC38

3

GND

5

VCC

0.1uF

C298

0

R397

UnPop

0

R398

UnPop

TP79

TP80

IC39

TC7SH14FU(TE85L.JF)

2

4

1

TC7SH14FU(TE85L.JF)

IC39

3

GND

5

VCC

0.1uF

C299

100

R200

2.2k

R217

2.2k

R400

UnPop

2.2k

R402

UnPop

2.2k

R401

220

R406

33

R414

UnPop

RA8

33

UnPop

1

8

6

5

4

3

2

7

RA132

33

UnPop

1

8

6

5

4

3

2

7

33

R415

UnPop

100

R417

100

R418

100

R419

100

R420

UnPop

0

R421

UnPop

2.2k

R423

UnPop

0

R436

0

R437

0

R439

0

R438

0

R441

UnPop

0

R440

UnPop

L506

BLM15BB121SN1D

EXB28V470JX

RA124

1

8

6

5

4

3

2

7

EXB28V470JX

RA125

1

8

6

5

4

3

2

7

EXB28V470JX

RA126

1

8

6

5

4

3

2

7

EXB28V470JX

RA127

1

8

6

5

4

3

2

7

KEY

TRACE

Half

Pitch

JTAG

(NC-PIN)

MODE setting

BMD2,BMD1,BMD0

000:16bit NOR FLASH boot

001:32bit NOR FLASH boot

010:SERIAL FLASH boot

011:Internal ROM (I2C boot)

Update mode

100:Internal ROM (SFI boot)

Normal mode

101:Internal ROM (Non boot)

110:Internal ROM (Non boot)

111:Internal ROM (Non boot)

TRCSEL

H:ETM Trace Enable

L:PA6-PA2(GPIO) Enable

TMODE

H:BOUNDARY-SCAN Enable

L:NORMAL Mode

TRCCKO:39MHz

SWD

to debug monitor