A

B

C

D

E

F

G

H

I

L

M

N

O

P

Q

R

S

T

U

J

K

1

2

3

4

5

6

7

8

9

10

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

23

11

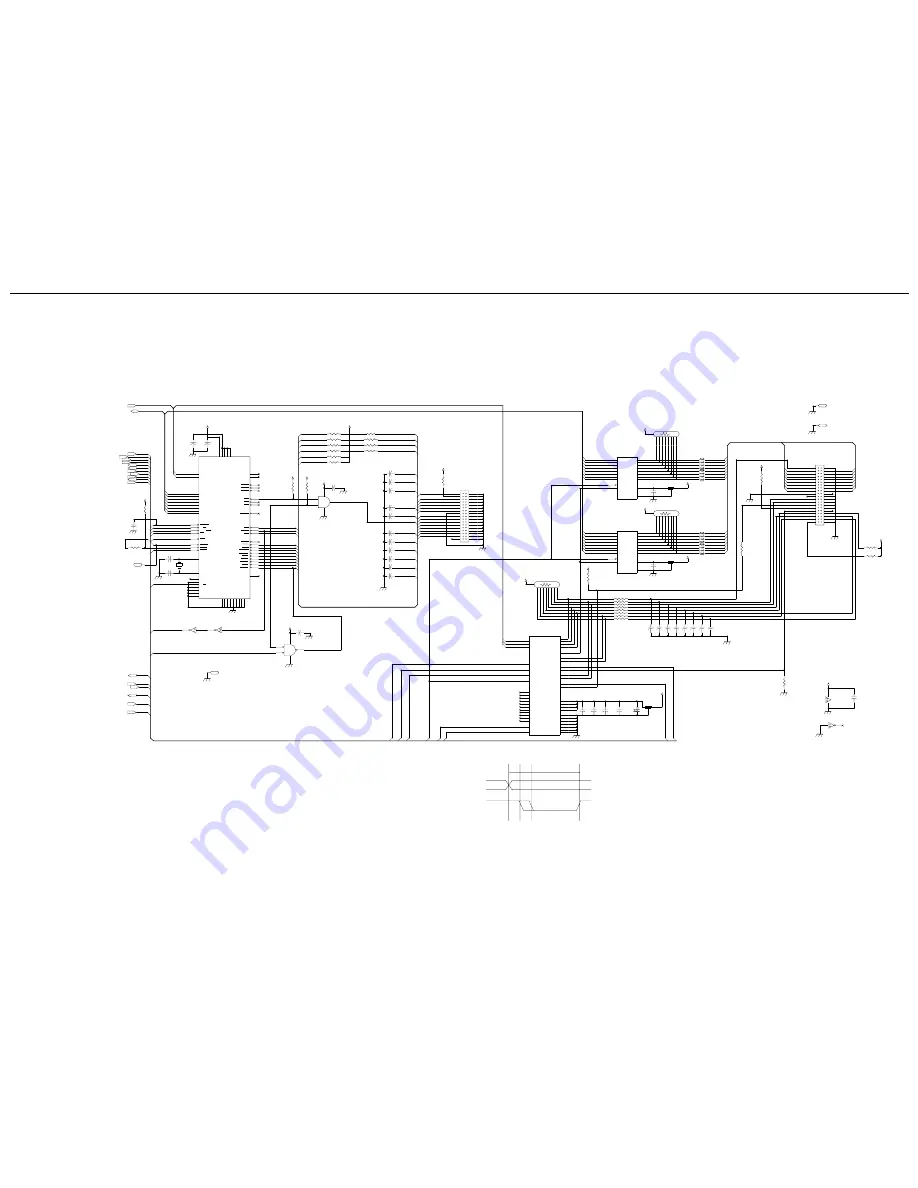

VA-7

July, 2000

ADDRESS BUS

DATA BUS

TO FDD UNIT PC/AT

XREADY

IDE

TO ZIP IDE

30ns

70ns

165ns

250ns

wait states =(3+1)*50ns + 1 cycle = 250ns

add

wrl/xrd

FDS3

XINDEX

XINP

XINP

XINDEX

XINP

FDS3

XINDEX

XFDCRST

XINP

XWRL

XINDEX

XFDC

XDS0

XDACK1

XFDCINT

XDREQ1

XFDCDEND

XIDXINT

RDYCNTL

IDEXRST

IDEXWRL

IDEXRD

IDEA3

XRDATA

XWDATA

FDS0

XRDATA

D10

FDS1

D7

D4

IDEA1

D0

D3

D7

D11

XTRK0

D13

IDECS0

XHDIR

FDS1

XTRK0

XSTEP

XSTEP

D8

XHSEL

D12

XRDATA

D14

XTRK0

D4

D2

XWPRT

IDEINT

XWDATA

XHDIR

D1

D3

D15

XHSEL

XWGATE

D5

D5

XWGATE

D0

XWPRT

XWPRT

D6

D2

D9

FDS1

XDS3

D6

D1

XHSEL

FDS0

XWPRT

XTRK0

XWGATE

FDS1

XHDIR

IDEIORDY

XWDATA

XSTEP

XRDATA

IDEA2

XRD

A18

IDECS1

FDS2

FDCCONT

FDS2

XREADY

XREADY

XRD

XWRL

A3

A1

A2

A1

A0

XIDEINT

IDEXWRL

IDEXRD

IDEA2

IDECS0

IDEXRST

IDEA1

IDEA3

IDECS1

20MHz

GWAITIN

XIDE

XRST

XIDE

XIDE

IDE9

IDE11

IDE15

IDE10

IDE7

IDE4

IDE1

IDE12

IDE8

IDE0

IDE3

IDE4

IDE2

IDE13

IDE12

IDE9

IDE13

IDE6

IDE8

IDE14

IDE11

IDE5

IDE15

IDE0

IDE7

IDE2

IDE[0..15]

IDE1

IDE14

IDE6

IDE3

IDE5

IDE10

5VD

5VD

5VD

5VD

5VD

5VD

5VD

5VD

5VD

5VD

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

5VD

D

5VD

5VD

5VD

5VD

5VD

D

D

5VD

D

5VD

R67

0s

R69

10Ks

R76

10Ks

R81

10Ks

R82

10Ks

R83

10Ks

R74

1Ks

R75

1Ks

R79

1Ks

R78

1Ks

R77

1Ks

R73

NIU

R80

10Ks

X2

16MHz

TP

TP14

niu

RA38

4x33s

1

8

2

7

3

6

4

5

RA41

4x33s

1

8

2

7

3

6

4

5

R141

22Ks

R143

22Ks

R142

0s

NIU

RA39

8x1Ks

4

5

6

7

8

9

3

2

1

RA40

4x33s

1

8

2

7

3

6

4

5

C128

NIU

CN17

5

7

9

11

13

15

3

1

17

19

21

23

25

27

29

31

33

34

32

30

28

26

24

22

20

18

16

14

12

10

8

6

4

2

IC16

HD63266-FP-64A

9

8

19

18

17

16

15

14

13

12

3

4

5

6

21

20

7

22

39

40

36

37

1

2

28

26

27

38

43

63

62

61

58

57

56

52

30

34

55

60

51

50

48

47

33

32

35

53

31

24

25

29

44

45

46

10

11

23

41

42

49

54

59

64

RS1

RS0

D7

D6

D5

D4

D3

D2

D1

D0

RESET

E,RD

R/W,WR

CS

IRQ

DREQ

DACK

DEND

XTAL1

EXTAL1

XTAL2

EXTAL2

8"/5"

XTALSEL

IFS

NUM1

NUM2

NC

NC

MON3

MON2

MON1

DS3

DS2

DS1

HLOAD

INP

INDEX

DS0

MON0

HDIR

STEP

WDATA

WGATE

TRK0

WPRT

RDATA

HSEL

READY

1/2EX1

VCC1

SFORM

VCC2

VCC3

VCC4

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

C141

10pFs

C135

47pFs

C125

NIU

C123

100nFs

IC32

74VHC245F

2

18

3

17

4

16

5

15

6

14

7

13

8

12

9

11

19

1

10

20

A1

B1

A2

B2

A3

B3

A4

B4

A5

B5

A6

B6

A7

B7

A8

B8

G

DIR

GND

VCC

FL8

ELKS471FA

2

1

3

C120

100nFs

R145

22Ks

TP

TP9

niu

C142

10pFs

C129

NIU

C131

NIU

C124

NIU

CN22

5

7

9

11

13

15

3

1

17

19

21

23

25

27

29

31

33

35

37

39

40

38

36

34

32

30

28

26

24

22

20

18

16

14

12

10

8

6

4

2

C126

NIU

C134

47pFs

C132

NIU

IC31

74VHC245F

2

18

3

17

4

16

5

15

6

14

7

13

8

12

9

11

19

1

10

20

A1

B1

A2

B2

A3

B3

A4

B4

A5

B5

A6

B6

A7

B7

A8

B8

G

DIR

GND

VCC

C130

NIU

C122

100nFs

C133

NIU

C127

100nFs

C119

100nFs

IC14

TC7S32F

1

2

4

5

3

IC23A

TC7W14F

1

7

IC23D

TC7W14F

8

4

IC23C

TC7W14F

6

2

IC23B

TC7W14F

3

5

TP

TP18

niu

TP

TP17

niu

RA37

4x33s

1

8

2

7

3

6

4

5

RA36

8x1Ks

4

5

6

7

8

9

3

2

1

R71

10Ks

C159

100nFs

R170 100s

R171 100s

R172 120s

R173 120s

R174 120s

R175 100s

R176 100s

C208

47pFs

NIU

C209

47pFs

NIU

C210

47pFs

NIU

C211

47pFs

NIU

C212

47pFs

NIU

C213

47pFs

NIU

C214

47pFs

NIU

IC33

IDE-7032LC44-15

6

5

4

8

9

11

12

16

17

14

41

25

10

22

30

42

3

15

23

35

7

13

18

19

20

21

2

1

24

32

33

34

44

38

43

40

39

37

27

28

26

29

36

31

ADDIN0

ADDIN1

ADDIN2

IDEIORDY

IDEINT

A18

RDIN

WRIN

CSIDE

RESETN

IDECS1

IDECS0

GND

GND

GND

GND

VCC

VCC

VCC

VCC

NC

NC

NC

NC

NC

NC

GND

GND

NC

NC

NC

NC

GND

NC

CLK

ADDOUT0

ADDOUT1

ADDOUT2

RDOUT

WROUT

GWAITOUT

XIDEINT

BUFF_DIR

XRST_OUT

R169 33s

C207

47pFs

NIU

C215

100uF16s

FL10

ELKS471FA

2

1

3

IC15

TC7S08F

1

2

4

5

3

R183

10Ks

C182

100nFs

C181

100nFs

C183

100nFs

C180

100nFs

C179

100nFs

R168

10Ks

C121

10nFs

R68

10Ks

FL7

ELKS471FA

2

1

3

RA42

8x1Ks

4

5

6

7

8

9

3

2

1

RDYCNTL

FDCCONT

XDACK1

XDREQ1

XFDCINT

XFDC

XWRL

XRD

XFDCDEND

XIDEINT

XIDXINT

XRST

A[0..3]

D[0..15]

XFDCRST

GWAITIN

XIDE

A18

20MHz

CIRCUIT DIAGRAM (MAIN PCB ASSY/ FDC & IDE Contr. Block)