BDM-610000075

Rev B

Chapter 4: Using the cpuModule

69

Control Registers

CGT_Channel

: Selects the channel to be displayed in the Channel Gain Table Registers. See

SW_Trig

: Write a ‘1’ to generate a trigger to scan through the Channel Gain Table regardless of the state of the

“Go” bit. Will read ‘0’ while the scan is happening, and ‘1’ when completed.

GO:

Set to ‘1’ to begin continuous sampling based on the Pacer Clock.

Reset:

Write ‘1’ to reset all aAIO registers, including the “Clear” functions. Always reads ‘0’.

Clear:

Write ‘1’ to stop sampling, clear the Filters, and reset the Scatter-Gather and DMA Offset counters. Always

reads ‘0’.

Chx

: A ‘1’ indicates that an interrupt is pending from channel ‘x’ of the Channel Gain Table. This bit is set

regardless of CH_IRQ_ENA. This is a non-stick register, and will be cleared when the interrupt condition is cleared

in the Channel Gain Table.

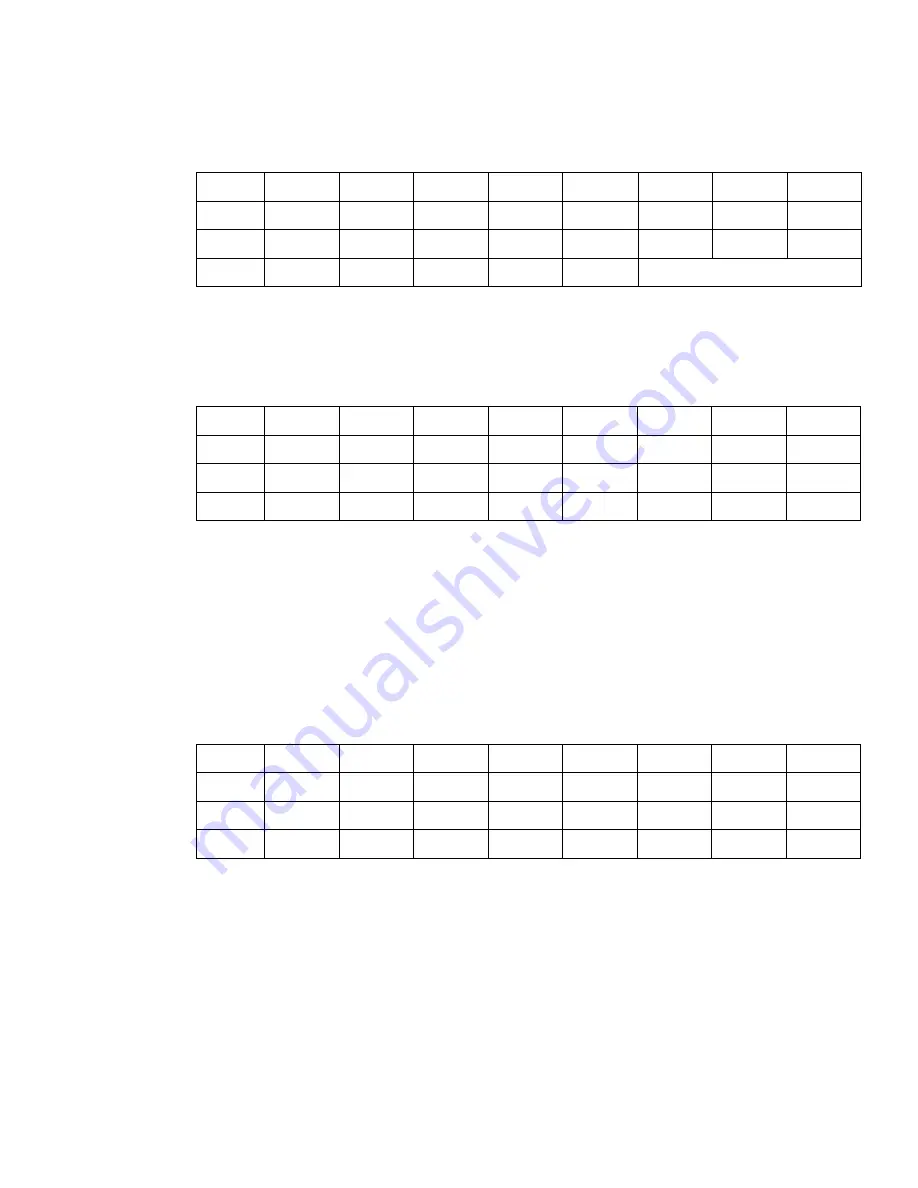

0x9E0: SELECT Register

Bit

7

6

5

4

3

2

1

0

Mode

R

R

R

R

R

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Field

Rsvd

Rsvd

Rsvd

Rsvd

Rsvd

CGT_Channel

0x9E1:

MODE_RESET Register

Bit

7

6

5

4

3

2

1

0

Mode

R/W

R/W

W

W

R/W

R/W

R/W

R/WC

Default

0

0

0

0

0

0

0

1

Field

Rsvd

Rsvd

Clear

Reset

Rsvd

Rsvd

GO

SW_Trig

0x9E2:

CH_IRQ_STAT Register

Bit

7

6

5

4

3

2

1

0

Mode

R

R

R

R

R

R

R

R

Default

0

0

0

0

0

0

0

0

Field

Ch8

Ch7

Ch6

Ch5

Ch4

Ch3

Ch2

Ch1

Summary of Contents for BDM-610000075

Page 3: ... Accessing the Analog World www rtd com ISO9001 and AS9100 Certified CMX32M cpuModules ...

Page 4: ...iv CMX32M cpuModule BDM 610000075 Rev B ...

Page 30: ...22 CMX32M cpuModule BDM 610000075 Rev B ...

Page 60: ...52 CMX32M cpuModule BDM 610000075 Rev B ...

Page 102: ...94 CMX32M cpuModule BDM 610000075 Rev B ...

Page 116: ...108 CMX32M cpuModule BDM 610000075 Rev B ...