84

CMX32M cpuModule

BDM-610000075

Rev B

Multi-Color LED

The CMX32M has a Multi-Color LED which can be enabled or disabled in the BIOS setup screen. The color of the

LED indicates the status of the board, as shown in Table 57.

The LED can also be controlled manually by writing to I/O Port 984h, as shown in Table 58 and Table 59

The following table lists the color displayed and the value written.

Table 57

LED Colors

Color

Description

Green

Normal Operation

Blue

SATA Activity

Red

cpuModule is in reset

1

1. If power is applied to the cpuModule while jumper

JP5

is installed, the LED will be red. This does not

indicate that the board is in reset

Yellow (Red + Green)

cpuModule is in Standby

White (R+G+B)

cpuModule is approaching thermal limit

2

2. The LED will remain White until the system is shut down.

Table 58

Multi-Color LED I/O Address 984h

D7

D6

D5

D4

D3

D2

D1

D0

Reserved Reserved Reserved Reserved

Reserved

Multi-Color

LED

Table 59

Manual LED Colors

I/O Port 984h Value

Color

0x00

Automatic (see Table 57)

0x08

Off (

will reduce system power consumption.)

0x09

Blue

0x0A

Green

0x0B

Cyan (Green + Blue)

0x0C

Red

0x0D

Magenta (Red + Blue)

0x0E

Yellow (Red + Green)

0x0F

White (Red + Green + Blue)

Summary of Contents for BDM-610000075

Page 3: ... Accessing the Analog World www rtd com ISO9001 and AS9100 Certified CMX32M cpuModules ...

Page 4: ...iv CMX32M cpuModule BDM 610000075 Rev B ...

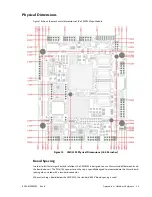

Page 30: ...22 CMX32M cpuModule BDM 610000075 Rev B ...

Page 60: ...52 CMX32M cpuModule BDM 610000075 Rev B ...

Page 102: ...94 CMX32M cpuModule BDM 610000075 Rev B ...

Page 116: ...108 CMX32M cpuModule BDM 610000075 Rev B ...