RTD Embedded Technologies, Inc.

| www.rtd.com

35

DM35418HR/DM35218HR

User’s Manual

BDM-610010041 Rev F

6.1

BAR0: General Board Control

This section contains the board-level interrupt control, as well as a description of all of the Functional Blocks in BAR2. Most of the registers in

this section are Read-Only. Although a full implementation requires BAR0 to be 0x400 in length, most implementations will have a shorter

length.

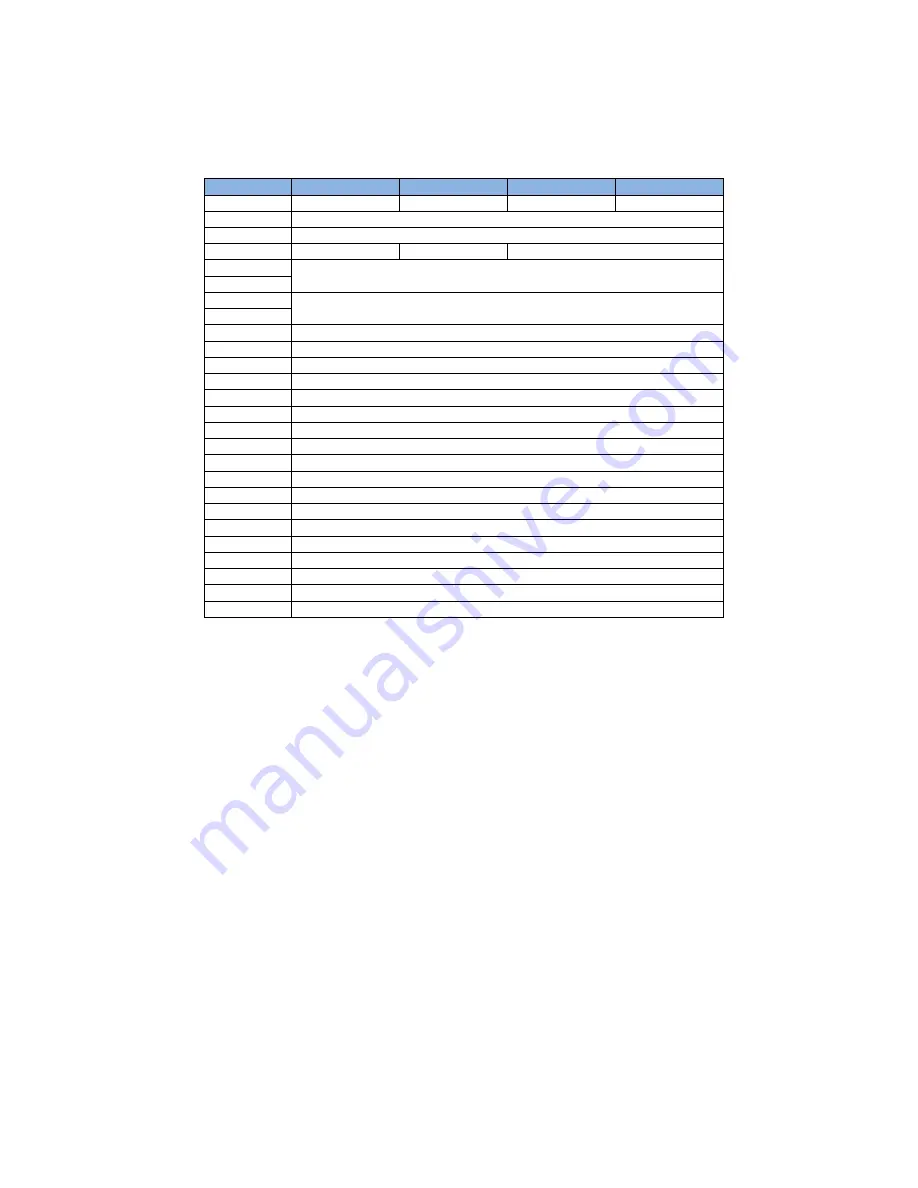

Table 19: Base Functional Block

Offset

0x03

0x02

0x01

0x00

0x00

GBC_BRD_RST

GBC_EOI

GBC_REV

GBC_FMT

0x04

GBC_PDP

0x08

GBC_BUILD

0x0C

Reserved

GBC_USER_ID

GBC_SYS_CLK_FREQ

0x10

GBC_IRQ_STATUS

0x14

0x18

GBC_DIRQ_STATUS

0x1C

0x20

FB0_ID

0x24

FB0_OFFSET

0x28

FB0_OFFSET_DMA

0x2C

reserved

0x30

FB1_ID

0x34

FB1_OFFSET

0x38

FB1_OFFSET_DMA

0x3C

reserved

…

0x20+0x10*n

FBn_ID

0x24+0x10*n

FBn_OFFSET

0x28+0x10*n

FBn_OFFSET_DMA

0x2C+0x10*n

reserved

…

0x3F0

FB61_ID

0x3F4

FB61_OFFSET

0x3F8

FB61_OFFSET_DMA

0x3FC

reserved

6.1.1

GBC_FMT

(R

EAD

-O

NLY

)

This register contains the format ID that is used in this board.

B[7:4] Major Format – Changes to this value indicate changes that are not backward compatible.

o

0 – Initial Major Format

B[3:0] Minor Format – Changes to this value indicate additional features that are backward compatible.

o

1 – Initial Minor Format

o

2 – Addition of FB_DMAm_CTRLn[Pause] flag and Early DMA Buffer Termination.

6.1.2

GBC_REV

(R

EAD

-O

NLY

)

This register contains the PDP revision for this board. A=1, B=2, etc.

6.1.3

GBC_BRD_RST

(R

EAD

/W

RITE

)

Write a value of 0xAA to this register to reset the board.

6.1.4

GBC_PDP

(R

EAD

-O

NLY

)

This register contains the PDP number for this board in decimal.

6.1.5

GBC_BUILD

(R

EAD

-O

NLY

)

Unique 32-bit build number for every FPGA build.

6.1.6

GBC_SYS_CLK_FREQ

(R

EAD

O

NLY

)

The measured frequency of the system clock. Units are 10 kHz, i.e. (Frequency in Hertz) = (GBC_SYS_CLK_FREQ * 10 kHz). This is

measured once after any reset, including GBC_BRD_RST. This value is not available (will read 0) until 100us after reset.