Saia-Burgess

Controls Ltd.

Hardware Manual for the PCD3 Series│Document 26/789; Version E 5│31.01.2005

Hardware

PCD3.H100

5-77

5

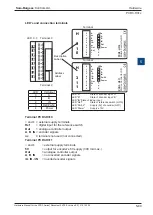

Block diagram

Operating principle

This can be largely derived from the logic diagram. It is only necessary to add some

explanation about the counter output circuit:

The output of the internal counter is identified as “Counter Flag”. The user has no

hardware access to it. This counter flag is set to “1” whenever the counter is loaded

or by means of a separate instruction.

The flag is “0”:

in up-counting mode:

when counter value 65’ 535 is reached

in down-counting mode:

when counter value 0 is reached

To reset a CCO hardware output which had previously been set high by the user

program, it is necessary to differentiate between two cases:

a) count range between 0...65,535 (normal case)

b) count range exceeding 65,535

Case a)

Resetting the counter flag results in a simultaneous reset of the CCO

output.

The “Reset Enable” should be activated

before

the counter reaches zero.

Eingangs-

Interface

Ausgangs-

Interface

Counter

Counter Flag

Counter enable

Counter Mode

(Decoding GAL)

up/down

Clock

Set

Set CCO

U+

CCO

P

C

D

-.

B

U

S

Eingangs-

filter

Eingänge

A

B

SC x1 x2 Modi

Counter Status Flag

Counter Flag

Reset Enable

CCO

0

50'000