KS57C2308/P2308/C2316/P2316

SAM47 INSTRUCTION SET

5-7

OPCODE DEFINITIONS

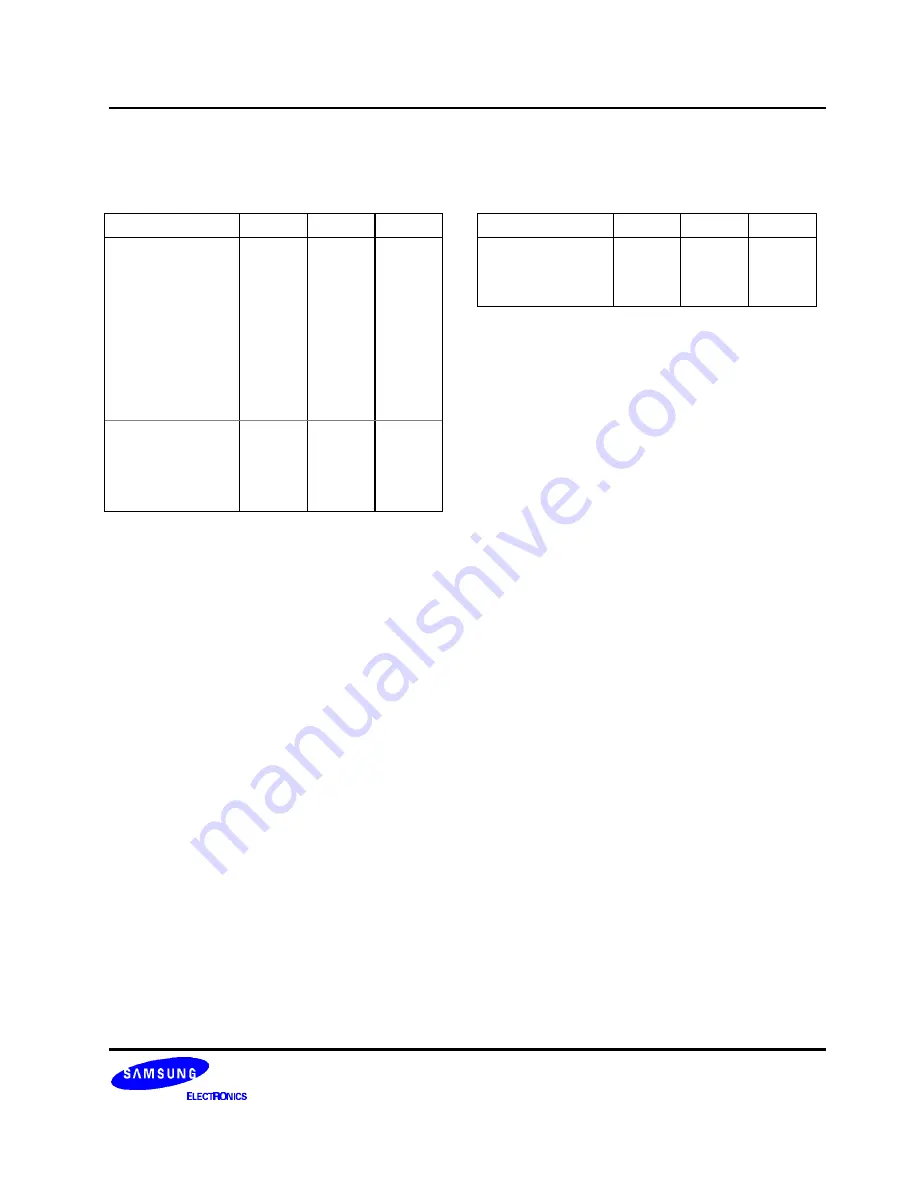

Table 5-7. Opcode Definitions (Direct)

Register

r2

r1

r0

A

0

0

0

E

0

0

1

L

0

1

0

H

0

1

1

X

1

0

0

W

1

0

1

Z

1

1

0

Y

1

1

1

EA

0

0

0

HL

0

1

0

WX

1

0

0

YZ

1

1

0

r

= Immediate data for register

Table 5-8. Opcode Definitions (Indirect)

Register

i2

i1

i0

@HL

1

0

1

@WX

1

1

0

@WL

1

1

1

CALCULATING ADDITIONAL MACHINE CYCLES FOR SKIPS

A machine cycle is defined as one cycle of the selected CPU clock. Three different clock rates can be selected

using the PCON register.

In this document, the letter “S” is used in tables when describing the number of additional machine cycles

required for an instruction to execute, given that the instruction has a skip function (“S” = skip). The addition

number of machine cycles that will be required to perform the skip usually depends on the size of the instruction

being skipped — whether it is a 1-byte, 2-byte, or 3-byte instruction. A skip is also executed for SMB and SRB

instructions.

The values in additional machine cycles for “S” for the three cases in which skip conditions occur are as follows:

Case 1: No skip

S = 0 cycles

Case 2: Skip is 1-byte or 2-byte instruction

S = 1 cycle

Case 3: Skip is 3-byte instruction

S = 2 cycles

NOTE

: REF instructions are skipped in one machine cycle.

i

= Immediate data for indirect addressing

Summary of Contents for C2316

Page 30: ...ADDRESS SPACES KS57C2308 P2308 C2316 P2316 2 22 NOTES ...

Page 168: ...SAM47 INSTRUCTION SET KS57C2308 P2308 C2316 P2316 5 94 NOTES ...

Page 170: ......

Page 206: ...POWER DOWN KS57C2308 P2308 C2316 P2316 8 8 NOTES ...

Page 210: ...RESET KS57C2308 P2308 C2316 P2316 9 4 NOTES ...

Page 222: ...I O PORTS KS57C2308 P2308 C2316 P2316 10 12 NOTES ...

Page 272: ...LCD CONTROLLER DRIVER KS57C2308 P2308 C2316 P2316 12 24 NOTES ...

Page 280: ...SERIAL I O INTERFACE KS57C2308 P2308 C2316 P2316 13 8 NOTES ...

Page 294: ...MECHANICAL DATA KS57C2308 P2308 C2316 P2316 15 2 NOTES ...

Page 310: ...KS57P2308 P2316 OTP KS57C2308 P2308 C2316 P2316 16 16 NOTES ...

Page 318: ......

Page 320: ......

Page 322: ......

Page 325: ......

Page 327: ......