KS57C2308/P2308/C2316/P2316

SAM47 INSTRUCTION SET

5-57

JPS

— Jump (Short)

JPS

dst

Operation:

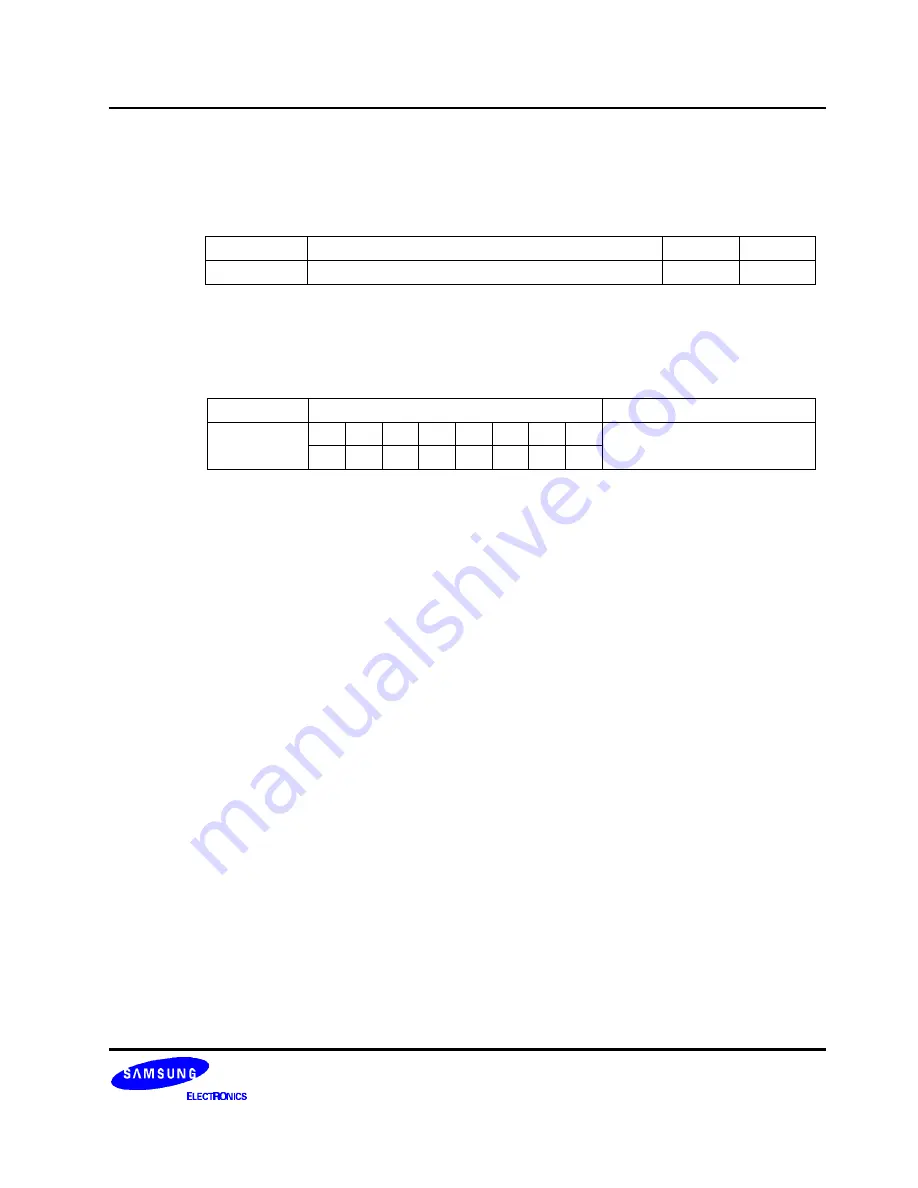

Operand

Operation Summary

Bytes

Cycles

ADR12

Jump direct in page (12 bits)

2

2

Description:

JPS causes an unconditional branch to the indicated address with the 4 K byte program memory

address space. Bits 0–11 of the program counter are replaced with the directly specified address.

The destination address for this jump is specified to the assembler by a label or by an actual

address in program memory.

Operand

Binary Code

Operation Notation

ADR12

1

0

0

1

a11

a10

a9

a8

PC13–12

←

PC13–12

a7

a6

a5

a4

a3

a2

a1

a0

PC11–0

←

ADR11–0

Example:

The label “SUB” is assigned to the instruction at program memory location 00FFH. The

instruction

JPS

SUB

at location 0EABH will load the program counter with the value 00FFH. Normally, the JPS

instruction jumps to the address in the block in which the instruction is located. If the first byte of

the instruction code is located at address xFFEH or xFFFH, the instruction will jump to the next

block. If the instruction “JPS SUB” were located instead at program memory address 0FFEH or

0FFFH, the instruction “JPS SUB” would load the PC with the value 10FFH, causing a program

malfunction.

Summary of Contents for KS57C2308

Page 30: ...ADDRESS SPACES KS57C2308 P2308 C2316 P2316 2 22 NOTES ...

Page 168: ...SAM47 INSTRUCTION SET KS57C2308 P2308 C2316 P2316 5 94 NOTES ...

Page 170: ......

Page 206: ...POWER DOWN KS57C2308 P2308 C2316 P2316 8 8 NOTES ...

Page 210: ...RESET KS57C2308 P2308 C2316 P2316 9 4 NOTES ...

Page 222: ...I O PORTS KS57C2308 P2308 C2316 P2316 10 12 NOTES ...

Page 272: ...LCD CONTROLLER DRIVER KS57C2308 P2308 C2316 P2316 12 24 NOTES ...

Page 280: ...SERIAL I O INTERFACE KS57C2308 P2308 C2316 P2316 13 8 NOTES ...

Page 294: ...MECHANICAL DATA KS57C2308 P2308 C2316 P2316 15 2 NOTES ...

Page 310: ...KS57P2308 P2316 OTP KS57C2308 P2308 C2316 P2316 16 16 NOTES ...

Page 318: ......

Page 320: ......

Page 322: ......

Page 325: ......

Page 327: ......