OSCILLATOR CIRCUITS

KS57C2308/P2308/C2316/P2316

6-10

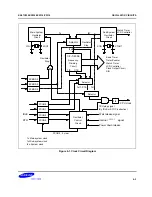

SWITCHING THE CPU CLOCK

Together, bit settings in the power control register, PCON, and the system clock mode register, SCMOD,

determine whether a main system or a subsystem clock is selected as the CPU clock, and also how this

frequency is to be divided. This makes it possible to switch dynamically between main and subsystem clocks and

to modify operating frequencies.

SCMOD.3, SCMOD.2, and SCMOD.0 select the main system clock (fx) or a subsystem clock (fxt) and start or

stop main or sub system clock oscillation. PCON.1 and PCON.0 control the frequency divider circuit, and divide

the selected fx clock by 4, 8, 64, or fxt clock by 4.

NOTE

A clock switch operation does not go into effect immediately when you make the SCMOD and PCON

register modifications — the previously selected clock continues to run for a certain number of machine

cycles.

For example, you are using the default CPU clock (normal operating mode and a main system clock of fx/64)

and you want to switch from the fx clock to a subsystem clock and to stop the main system clock. To do this, you

first need to set SCMOD.0 to "1". This switches the clock from fx to fxt but allows main system clock oscillation

to continue. Before the switch actually goes into effect, a certain number of machine cycles must elapse. After

this time interval, you can then disable main system clock oscillation by setting SCMOD.3 to "1".

This same “stepped” approach must be taken to switch from a subsystem clock to the main system clock: first,

clear SCMOD.3 to "0" to enable main system clock oscillation. Until main osc is stabilized, system clock must not

be changed. Then, after a certain number of machine cycles has elapsed, select the main system clock by

clearing all SCMOD values to logic zero.

After

RESET

, CPU operation starts with the lowest main system clock frequency of 15.3 µs at 4.19 MHz after the

standard oscillation stabilization interval of 31.3 ms has elapsed. Table 6-6 details the number of machine cycles

that must elapse before a CPU clock switch modification goes into effect.

Summary of Contents for KS57C2308

Page 30: ...ADDRESS SPACES KS57C2308 P2308 C2316 P2316 2 22 NOTES ...

Page 168: ...SAM47 INSTRUCTION SET KS57C2308 P2308 C2316 P2316 5 94 NOTES ...

Page 170: ......

Page 206: ...POWER DOWN KS57C2308 P2308 C2316 P2316 8 8 NOTES ...

Page 210: ...RESET KS57C2308 P2308 C2316 P2316 9 4 NOTES ...

Page 222: ...I O PORTS KS57C2308 P2308 C2316 P2316 10 12 NOTES ...

Page 272: ...LCD CONTROLLER DRIVER KS57C2308 P2308 C2316 P2316 12 24 NOTES ...

Page 280: ...SERIAL I O INTERFACE KS57C2308 P2308 C2316 P2316 13 8 NOTES ...

Page 294: ...MECHANICAL DATA KS57C2308 P2308 C2316 P2316 15 2 NOTES ...

Page 310: ...KS57P2308 P2316 OTP KS57C2308 P2308 C2316 P2316 16 16 NOTES ...

Page 318: ......

Page 320: ......

Page 322: ......

Page 325: ......

Page 327: ......