KS8910 100/10 Mbps ETHERNET TRANSCEIVER

FINCTIONAL BLOCKS

3-1

Preliminary Spec. ver

1.4

3

FUNCTIONAL BLOCKS

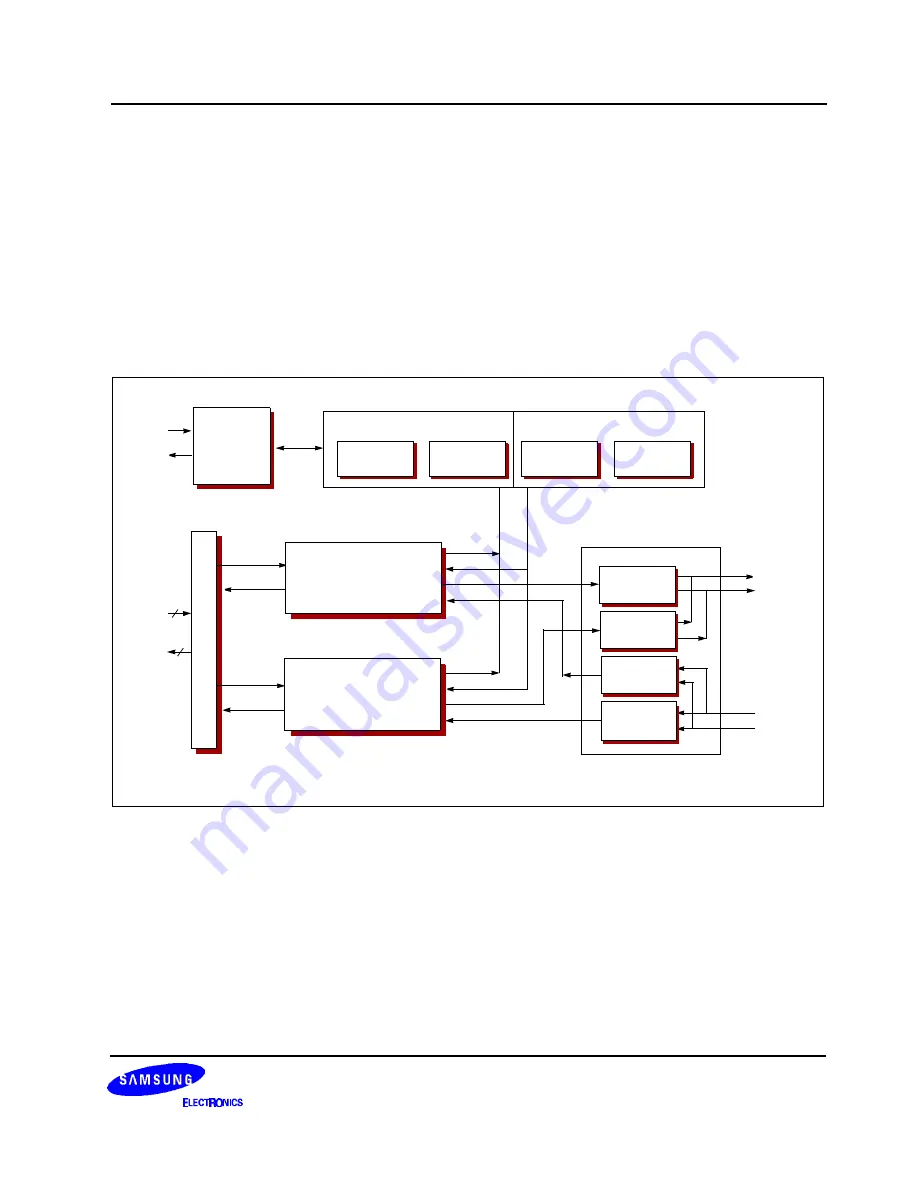

This section of the specification provides a description of the functional blocks of the KS8910 10/100 Mbit/s

Ethernet Transceiver architecture. The next Chapter of the document will describe the blocks in detail. Shown in

Figure 3-1

are the functional blocks in the architecture.

MII DATA INTERFACE

The purpose of the MII data interface is to provide a simple, inexpensive, and easily implemented interconnection

between the Media Access Control (MAC) sublayer and Physical (PHY) layer devices and between PHY layer

devices and Station Management. The MII interface provides a uniform interface to the Reconciliation Sublayer for

all 100Base-T physical layer device implementation. Services required by the MII include the following:

Figure 3-1. Functional Block Diagram of KS8910

Auto-Negotiation

20MHz

L

in

k

S

ta

tu

s

L

in

k

C

o

n

tr

o

l

+

TX

-

MI

Station

MGM

Interface

Control

Registers

Status

Registers

Power

Management

Auto-neg

Arbitration

10 Base-T

10/20MHz

Fast Ethernet

100 Base-TX

25MHz/125MHz

M

ll

D

a

ta

I

n

te

rf

a

c

e

Driver

MLT3

Driver

100RX

10RX

Registers

+

RX

-

TX

RX

MDC

MDIO

20MHz

4

4

Summary of Contents for KS8910

Page 1: ...20 8910 0599 USER S MANUAL KS8910 100 10 Mbps Ethernet Transceriver PHY Preliminary ...

Page 4: ...PRELIMINARY SPECIFICATION vi KS8910 100 10 Mbps ETHERNET CONTROLLER ...

Page 21: ...EXTERNAL SIGNALS KS8910 100 10 Mbps ETHERNET TRANSCEIVER 2 8 Preliminary Spec ver 1 4 MEMO ...

Page 89: ...APPLICATION NOTE KS8910 100 10 Mbps ETHERNET TRANSCEIVER 9 2 Preliminary Spec ver 1 4 MEMO ...

Page 91: ...MECHANICAL DATA KS8910 100 10 Mbps ETHERNET TRANSCEIVER 10 2 Preliminary Spec ver 1 4 MEMO ...

Page 99: ...A 8 APPENDIX KS8910 100 10 Mbps ETHERNET TRANSCEIVER Preliminary Spec ver 1 4 NOTES ...