S3C80A5B

RESET

and POWER-DOWN

8-1

8

RESET

and POWER-DOWN

SYSTEM RESET

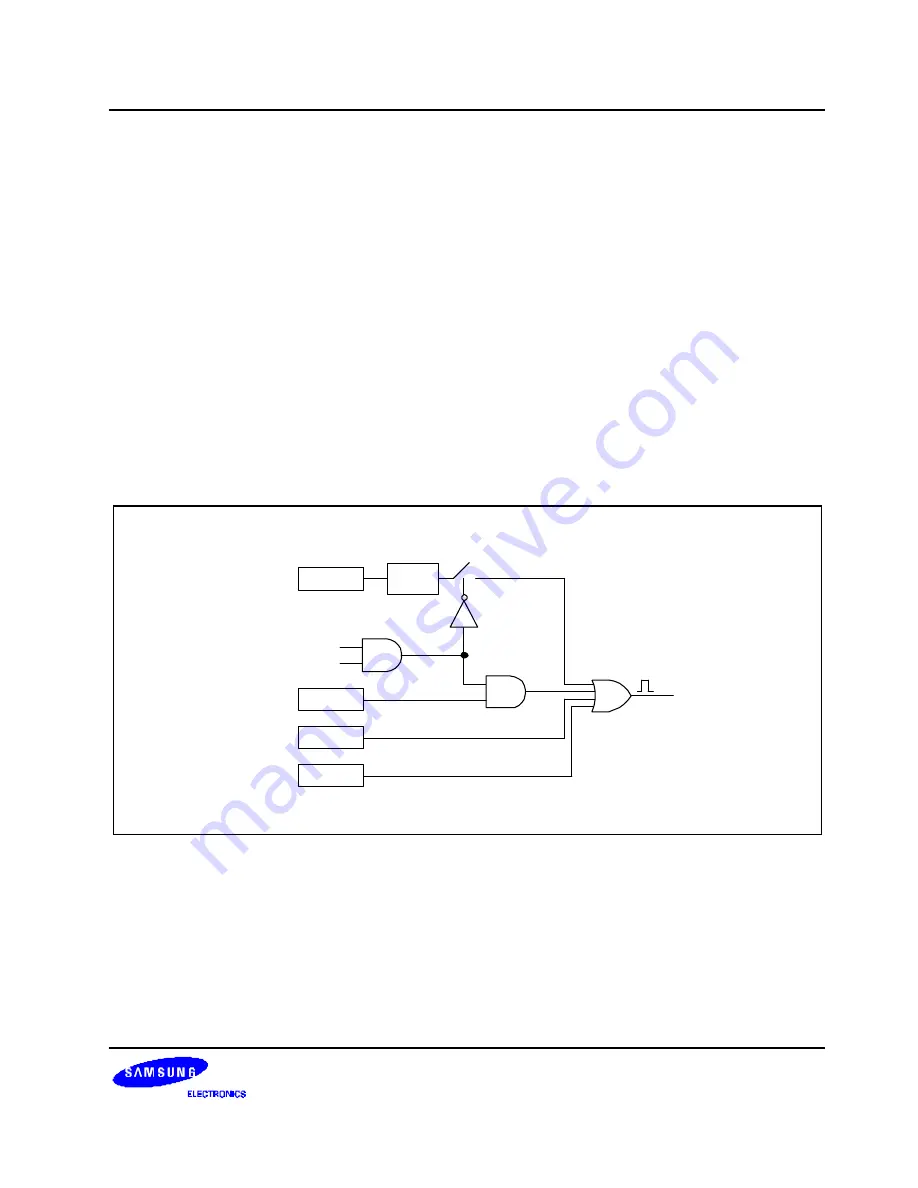

S3C80A5B has four different system reset sources as followings:

— Low Voltage Detect (LVD)

— Internal POR circuit

— INTR (Interrupt with RESET)

— Basic Timer (Watchdog timer)

STOPCON

Noise

Filter

LVD

Stop

INTR

POR

BT(WDT)

Enable/Disable

Figure 8-1. Rese t Block Diagram

LVD RESET

The Low Voltage detect circuit is built on the S3C80A5B product for system reset not in stop mode. When the

operating status is not stop mode it detects a slope of V

DD

by comparing the voltage at V

DD

with V

LVD

(Low level

Detect Voltage). The reset pulse is generated by the rising slope of V

DD

. While the voltage at V

DD

is rising up and

passing V

LVD

, the reset pulse is occurred at the moment ”V

DD

>=

V

LVD

". This function is disabled when the

operating state is "stop mode" to reduce the current consumption under 1 uA instead of 6 uA.