CONTROL REGISTERS

S3C80A5B

4-10

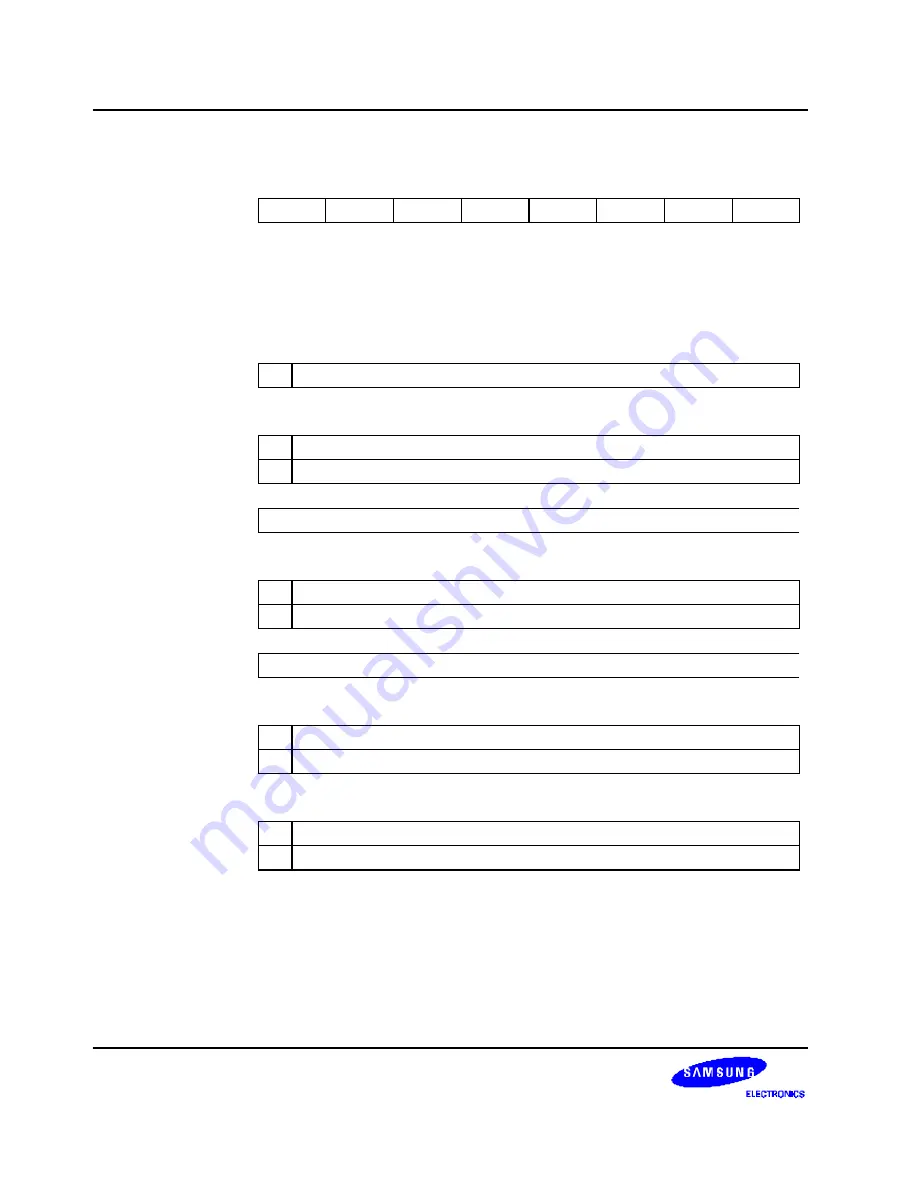

IMR

— Interrupt Mask Register

DDH

Set 1

Bit Identifier

.7

.6

.5

.4

.3

.2

.1

.0

RESET Value

x

x

x

x

x

x

x

x

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Addressing Mode

Register addressing mode only

.7

Interrupt Level 7 (IRQ7) Enable Bit; External Interrupts P0.7–P0.4

1

Enable (un-mask)

.6

Interrupt Level 6 (IRQ6) Enable Bit; External Interrupts P0.3–P0.0

0

Disable (mask)

1

Enable (un-mask)

.5

Not used for S3C80A5B.

.4

Interrupt Level 4 (IRQ4) Enable Bit; Counter A Interrupt

0

Disable (mask)

1

Enable (un-mask)

.3–.2

Not used for S3C80A5B.

.1

Interrupt Level 1 (IRQ1) Enable Bit; Timer 1 Match or Overflow

0

Disable (mask)

1

Enable (un-mask)

.0

Interrupt Level 0 (IRQ0) Enable Bit; Timer 0 Match or Overflow

0

Disable (mask)

1

Enable (un-mask)

NOTES:

1. When an interrupt level is masked, any i nterrupt requests that may be issued are not recognized by the CPU.

2. Interrupt levels IRQ2, IRQ3 and IRQ5 are not used in the S3C80A5B interrupt structure.