S3C80A5B

INTERRUPT STRUCTURE

5-7

ENABLE/DISABLE INTERRUPT INSTRUCTIONS (EI, DI)

Executing the Enable Interrupts (EI) instruction globally enables the interrupt structure. All interrupts are then

serviced as they occur, and according to the established priorities.

NOTE

The system initialization routine that is executed following a reset must always contain an EI instruction to

globally enable the interrupt structure.

During normal operation, you can execute the DI (Disable Interrupt) instruction at any time to globally disable

interrupt processing. The EI and DI instructions change the value of bit 0 in the SYM register. Although you can

manipulate SYM.0 directly to enable or disable interrupts, we recommend that you use the EI and DI instructions

instead.

SYSTEM-LEVEL INTERRUPT CONTROL REGISTERS

In addition to the control registers for specific interrupt sources, four system-level registers control interrupt

processing:

— The interrupt mask register, IMR, enables (un-masks) or disables (masks) interrupt levels.

— The interrupt priority register, IPR, controls the relative priorities of interrupt levels.

— The interrupt request register, IRQ, contains interrupt pending flags for each interrupt level (as opposed to

each interrupt source).

— The system mode register, SYM, enables or disables global interrupt processing (SYM settings also enable

fast interrupts and control the activity of external interface, if implemented).

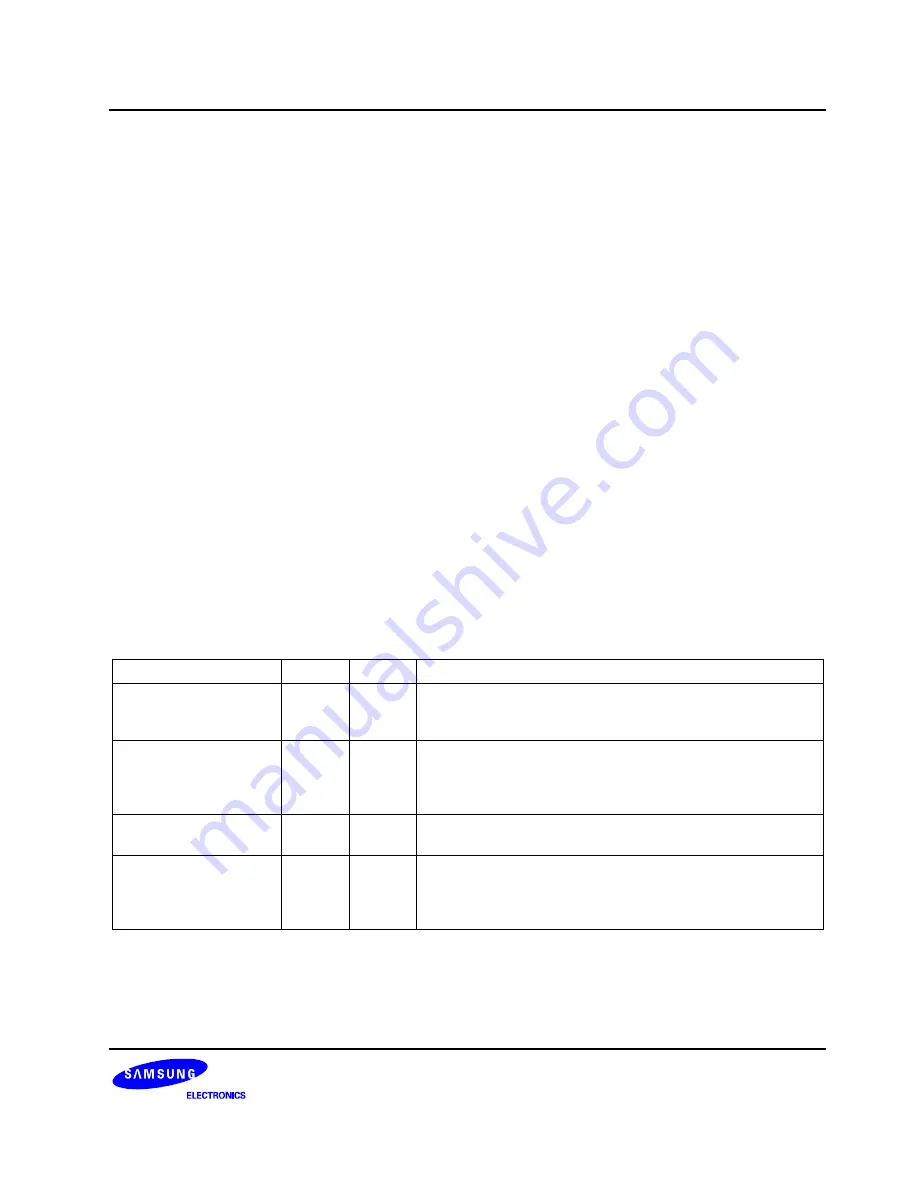

Table 5-2. Interrupt Control Register Overview

Control Register

ID

R/W

Function Description

Interrupt mask register

IMR

R/W

Bit settings in the IMR register enable or disable interrupt

processing for each of the five interrupt levels: IRQ0, IRQ1,

IRQ4, and IRQ6–IRQ7.

Interrupt priority register

IPR

R/W

Controls the relative processing priorities of the interrupt levels.

The five levels of the S3C80A5B are organized into three

groups: A, B, and C. Group A is IRQ0 and IRQ1, group B is

IRQ4, and group C is IRQ6, and IRQ7.

Interrupt request register

IRQ

R

This register contains a request pending bit for each interrupt

level.

System mode register

SYM

R/W

Dynamic global interrupt processing enable/ disable, fast

interrupt processing, and external interface control (An external

memory interface is not implemented in the S3C80A5B

microcontroller).