Summary of Contents for SF-335T

Page 2: ......

Page 19: ...CIRCUIT DESCRIPTION 2 Chorus 2 Assigned GPO Ports for RHINE ...

Page 21: ...CIRCUIT DESCRIPTION 5 HP IMPORTANT ASIC Ports for RHINE ...

Page 24: ...CIRCUIT DESCRIPTION 3 1 5 3 Block Diagram Figure 16 Block Diagram of IP_TOP ...

Page 35: ...CIRCUIT DESCRIPTION 3 1 8 6 FM214 MODEM BLOCK DIAGRAM 3 1 8 7 FM214 VS MODEM BLOCK DIAGRAM ...

Page 36: ...CIRCUIT DESCRIPTION 3 1 8 8 FM214 SERIES MODEM PIN DESCRIPTION ...

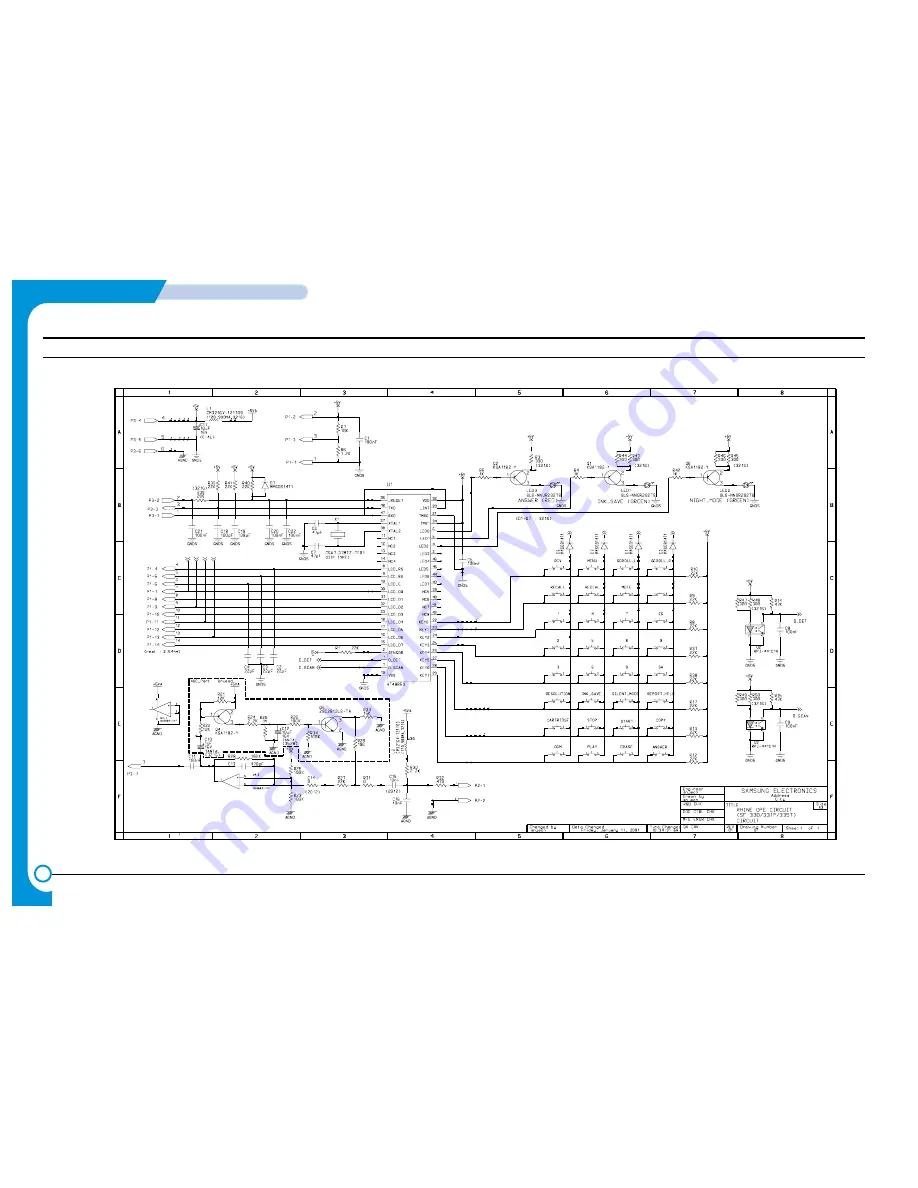

Page 48: ...4 5 Samsung Electronics SCHEMATIC DIAGRAMS Repair Manual 4 2 LIU Circuit Diagram 2002 06 25 ...