SAMSUNG Proprietary-Contents may change without notice

2. SGH-X430 Circuit Description

2-

2

This Document can not be used without Samsung's authorization

5. Si 4205 (U100)

This chip integrates three differential-input LNAs.

The GSM input supports the E-GSM, DCS input supports the DCS1800, PCS

input supports the PCS1900. The LNA

inputs are matched to the 200 ohm

differential output SAW filters through eternal LC matching network.

Image-reject mixer downconverts the RF signal to a 100 KHz intermediate

frequency(IF) with the RFLO from SI4133T frequency synthesizer.

The RFLO frequency is between 1737.8 ~ 1989.9 MHz.

The Mixer output is amplified with an analog programmable gain

amplifier(PGA), which is controlled by AGAIN.

The quadrature IF signal is digitized with high resolution A/D converts (ADC).

The SI4205 down-converts the ADC output to baseband with a digital

100 KHz quadrature LO signal.

Digital decimation and IIR filters perform channel selection to remove blocking

and reference interface signals. After channel selection, the digital output is

scaled with a digital PGA, which is controlled with the DGAIN. DACs drive a

differential analog signal onto the RXIP, RXIN, RXQP, RXQN pins to interface

to standard analog-input baseband IC.

2) TX PART

Baseband IQ signal fed into offset PLL, this function is included inside

of U100 chip.

SI4205 chip generates modulator signal which power level is about 1.5dBm

and fed into Power Amplifier(U200).

The PA output power and power ramping are well controlled by Auto

Power Control circuit. We use offset PLL below,

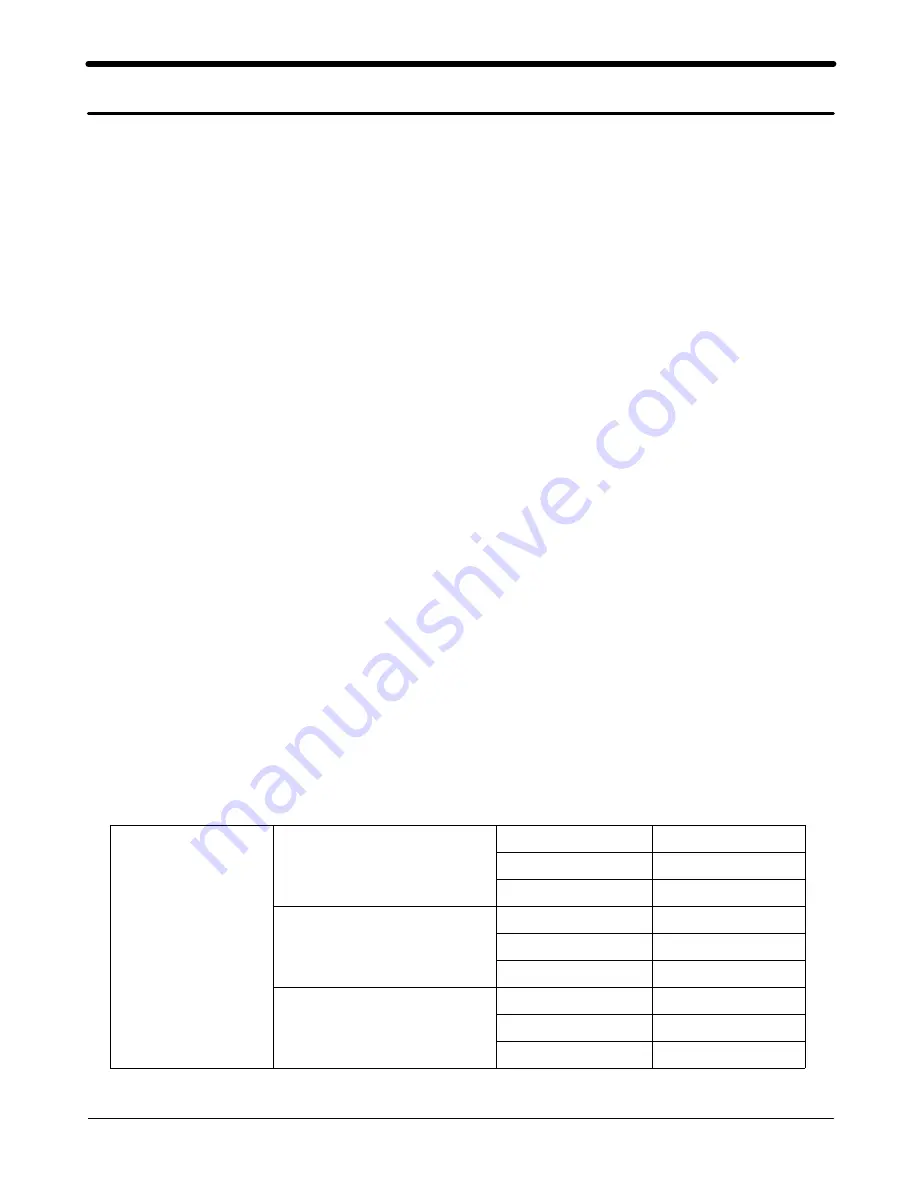

Modulation

Spectrum

200kHz offset

30 kHz bandwidth

GSM

-35dBc

DCS

-35dBc

PCS

-35dBc

400kHz offset

30 kHz bandwidth

GSM

-66dBc

DCS

-65dBc

PCS

-66dBc

600kHz ~ 1.8MHz offset

30 kHz bandwidth

GSM

-75dBc

DCS

-68dBc

PCS

-75dBc