2. Product Specifications and Description

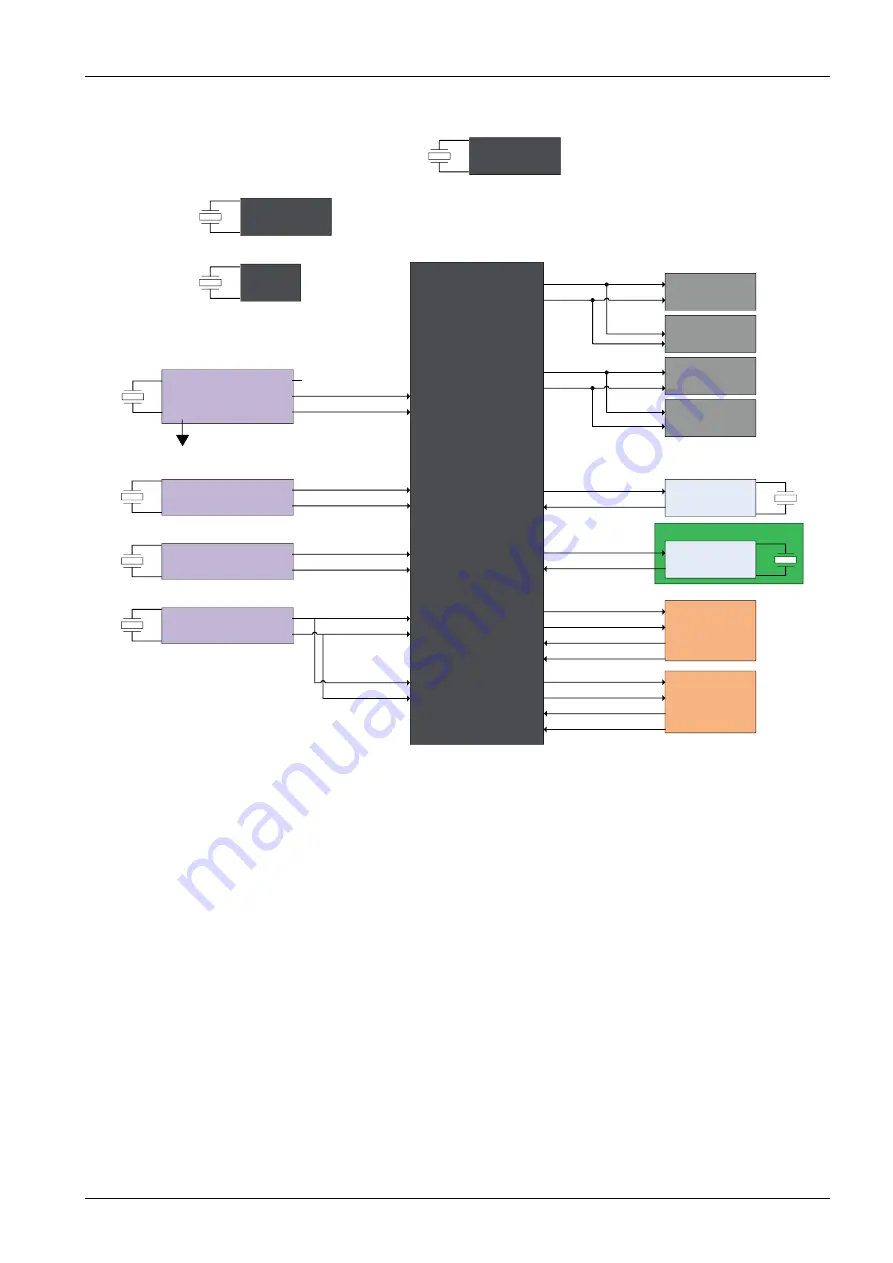

2) Main Controller Clock Diagram

N ETW O RK O PTIO N PBA

CLK_M A IN (Spread 12M hz)

CLK_PU RE(Reference 12M hz)

ASM 3P2863

Cl

k0

Cl

k2

Cl

k1

N .C

Sel

SA TA _REFCLK_P(100M hz)

SA TA _REFCLK_N

PL602-21

25M hz

Crystal

Input

Cl

k0

Cl

k1

PCI_REFCLK_P(100M hz)

PCI_REFCLK_N

PL602-21

25M hz

Crystal

Input

Cl

k0

Cl

k1

U SB3H _REFCLK_P(100M hz)

U SB3H _REFCLK_N

U SB3D _REFCLK_P(100M hz)

U SB3D _REFCLK_N

PL602-21

25M hz

Crystal

Input

Cl

k0

Cl

k1

D D R3 8G b

K4B8G 1646B

D D R3 8G b

K4B8G 1646B

D D R3 8G b

K4B8G 1646B

D D R3 8G b

K4B8G 1646B

CH 0_CLK_P(800M hz)

CH 0_CLK_N

CH 1_CLK_P(800M hz)

CH 1_CLK_N

N ETW O RK PH Y

RTL8211

M A C0_G TX_CLK(125M hz)

M A C0_RX_CLK(125M hz)

N ETW O RK PH Y

RTL8211

M A C1_G TX_CLK(125M hz)

M A C1_RX_CLK(125M hz)

12M hz

Crystal

Input

12M hz

Crystal

Input

12M hz

Crystal

Input

RTS5401

U SB3.0 H U B

12M hz

Crystal

Input

A TSA M D

20E15

CCD M

CLK_M A IN _CCD M _P(35M hz)

CLK_M A IN _CCD M _N

RX_CLK_CCD M _P(35M hz)

RX_CLK_CCD M _N

D CIS

CLK_M A IN _D CIS_P(35M hz)

CLK_M A IN _D CIS_N

RX_CLK_D CIS_P(35M hz)

RX_CLK_D CIS_N

12M hz

Crystal

Input

A3000

D D R3 C H 0

D D R3 C H 1

M AC 0

M AC 1

SC AN 0

SC AN 1

RTC

32.768Khz

Crystal Input

M 41T81

RTC w ith IRQ

Copyright© 1995-2013 SAMSUNG. All rights reserved.

2-101