MultiMediaCard Product Manual

SanDisk MultiMediaCard Product Manual Rev. 2 © 2000 SANDISK CORPORATION

48

5.7.2

Command Format

(

Command length 48 bits, 2.4

µ

s @ 20 MHz)

0

1

bit 5...bit 0

bit 31...bit 0

bit 6...bit 0

1

start bit

host

command

argument

CRC7

1

end bit

Commands and arguments are listed in Table 5-3 through Table 5-9.

7-bit CRC Calculation: G(x) = x

7 +

x

3 +

1

M(x) = (start bit)

∗

x

39

+ (host bit)

∗

x

38

+...+ (last bit before CRC)

∗

x

0

CRC[6...0] = Remainder[(M(x)

∗

x

7

)/G(x)]

5.7.3

Command Classes

The command set of the MultiMediaCard is divided into several classes (See Table 5-2). Each class

supports a set of MultiMediaCard functions.

The supported Card Command Classes (CCC) are coded as a parameter in the card specific data (CSD)

register of each card, providing the host with information on how to access the card.

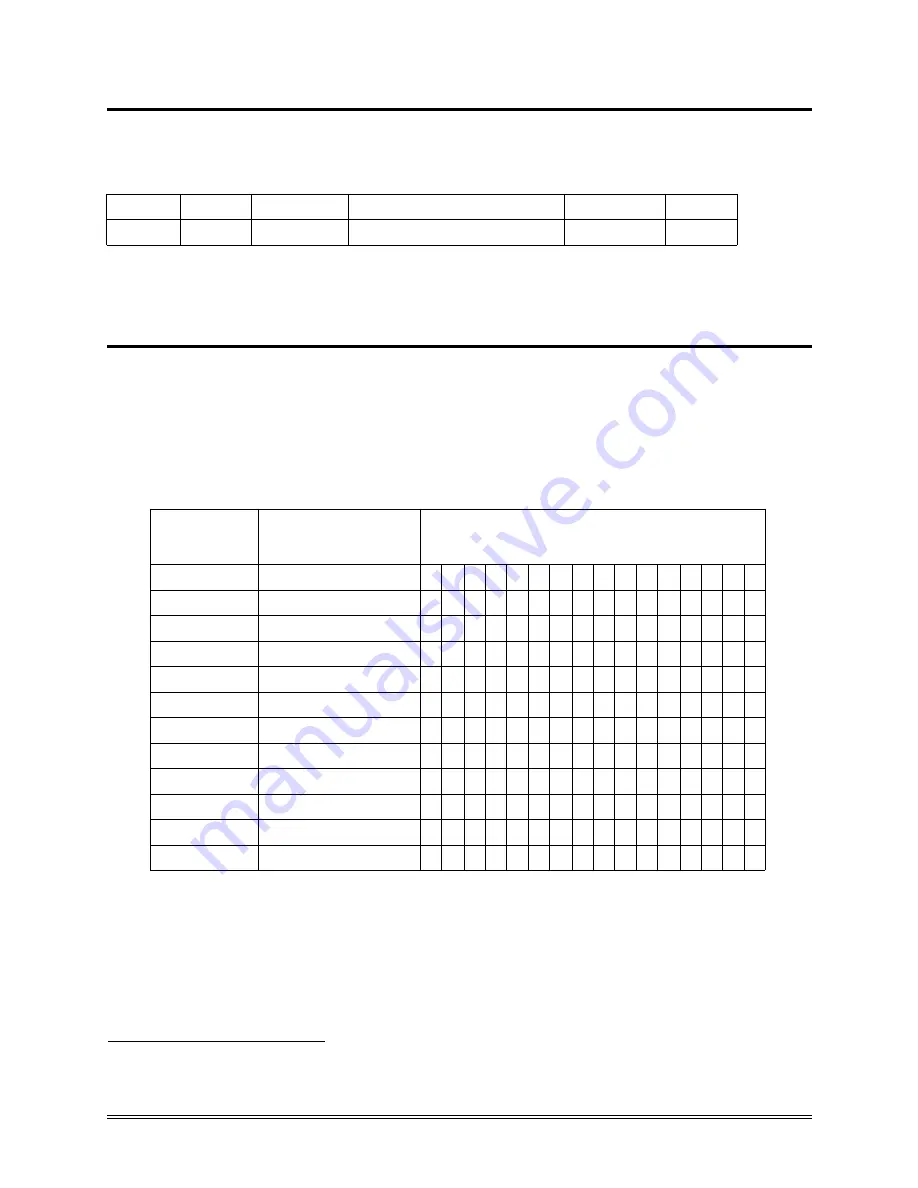

Table 5-2 Card Command Classes (CCCs)

C a r d

Command

Class (CCC)

Class Description

Supported Commands

0

1

2

3

4

7

9 10 11 12 13 15 16 17 18 20

Class 0

Basic

+

+

+

+

+

+

+

+

+

+

+

Class 1

Stream Read

+

Class 2

Block Read

+

+

+

Class 3

Stream Write

+

Class 4

Block Write

+

Class 5

Erase

Class 6

Write Write-Protection

Class 7

Read Write-Protection

Class 8

Erase Write-Protection

Class 9

I/O Mode

2

Class 10-11

Reserved

1)

7-bit Cyclic Redundancy Check.

2)

I/O mode class is not supported by the SanDisk MultiMediaCard.