Chapter 4 – SD Card Protocol Description

Revision 2.2

SanDisk SD Card Product Manual

© 2004 SanDisk Corporation

4-4

12/08/04

4.2 Functional

Description

The host (master) controls all communication between it and the SD Card. The host sends

the following two types of commands:

•

Broadcast Commands

— Broadcast commands are intended for all SD cards. Some of

these commands require a response.

•

Addressed (Point-to-Point) Commands

— The addressed commands are sent to the

addressed SD Card and cause a response to be sent from this card.

A general overview of the command flow is shown in Figure 4-7 for the Card Identification

Mode and in Figure 4-8 for the Data Transfer Mode. The commands are listed in Tables 4-

15 and 4-16. The dependencies among the current SD Card, received-command and

following states are listed in Table 4-18. In the following sections, the various card

operation modes will be described first. Thereafter, the restrictions for controlling the clock

signal are defined. All SD Card commands, together with corresponding responses, state

transitions, error conditions, and timings are presented in the following sections.

The SanDisk SD Card has two operation modes.

•

Card Identification Mode

— The host will be in card identification mode after reset

and while it is looking for new cards on the bus. SD cards will be in this mode after

reset until the SET_RCA command (CMD3) is received.

•

Data Transfer Mode

— SD cards will enter data-transfer mode when their RCA is first

published. The host will enter data-transfer mode after identifying all SD cards on the

bus.

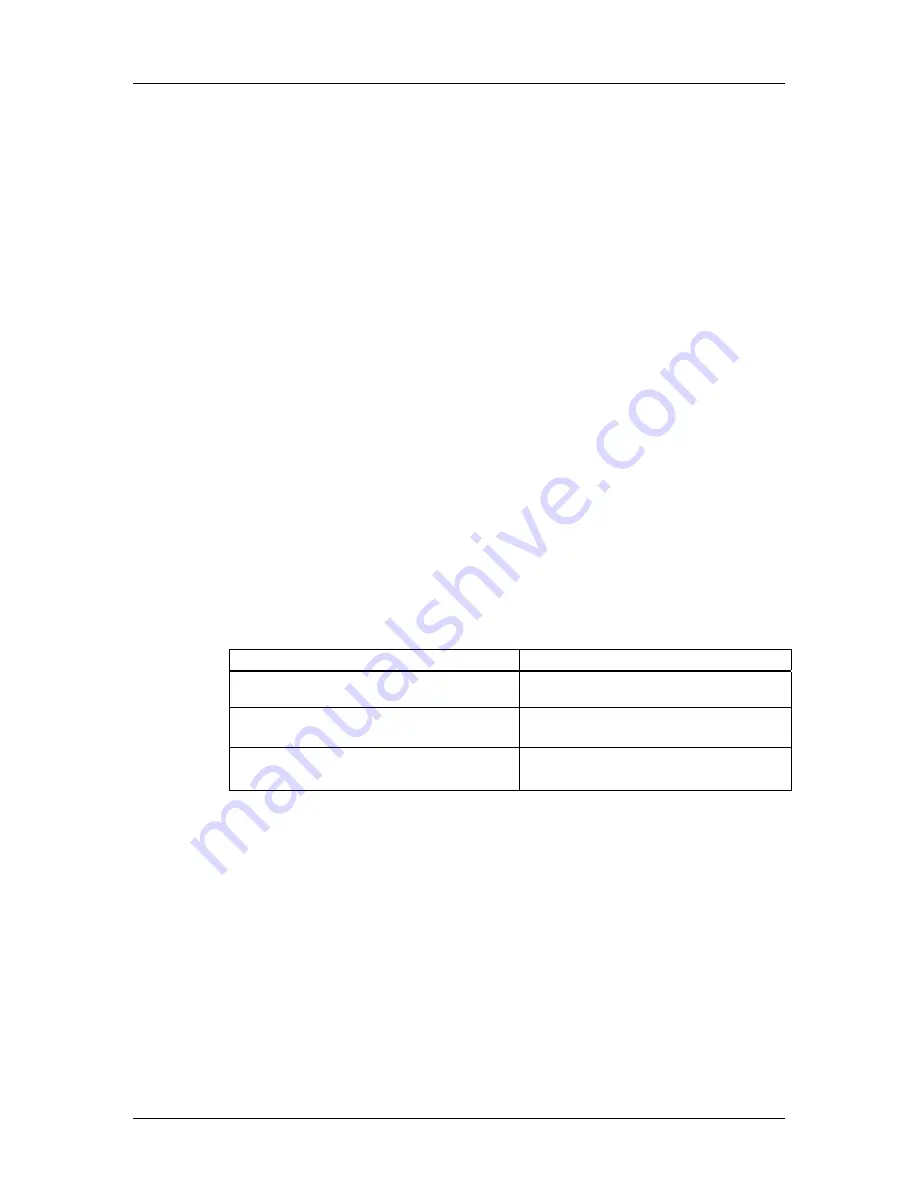

Table 4-1 lists the dependencies between operation modes and card states. Each state in the

card state diagrams (Figure 4-7 and 4-8) is associated with one operation mode.

Table 4-1

Card States vs. Operation Modes Overview

Card State

Operation Mode

Inactive Inactive

Idle, Ready, Identification

Card Identification Mode

Standby, Transfer, Send data, Receive data,

Programming, Disconnect

Data Transfer Mode

4.3

Card Identification Mode

In Card Identification Mode the host resets all cards, validates operation voltage range,

identifies and requests cards to publish a Relative Card Address (RCA). This operation is

performed on each card separately using its own command (CMD) line. All data

communication in the Card Identification Mode uses the CMD line only.