COMe-cVR6 – User Guide Rev. 1.5

// 31

SoC

COMe (3.3V)

SoC

COMe (3.3V)

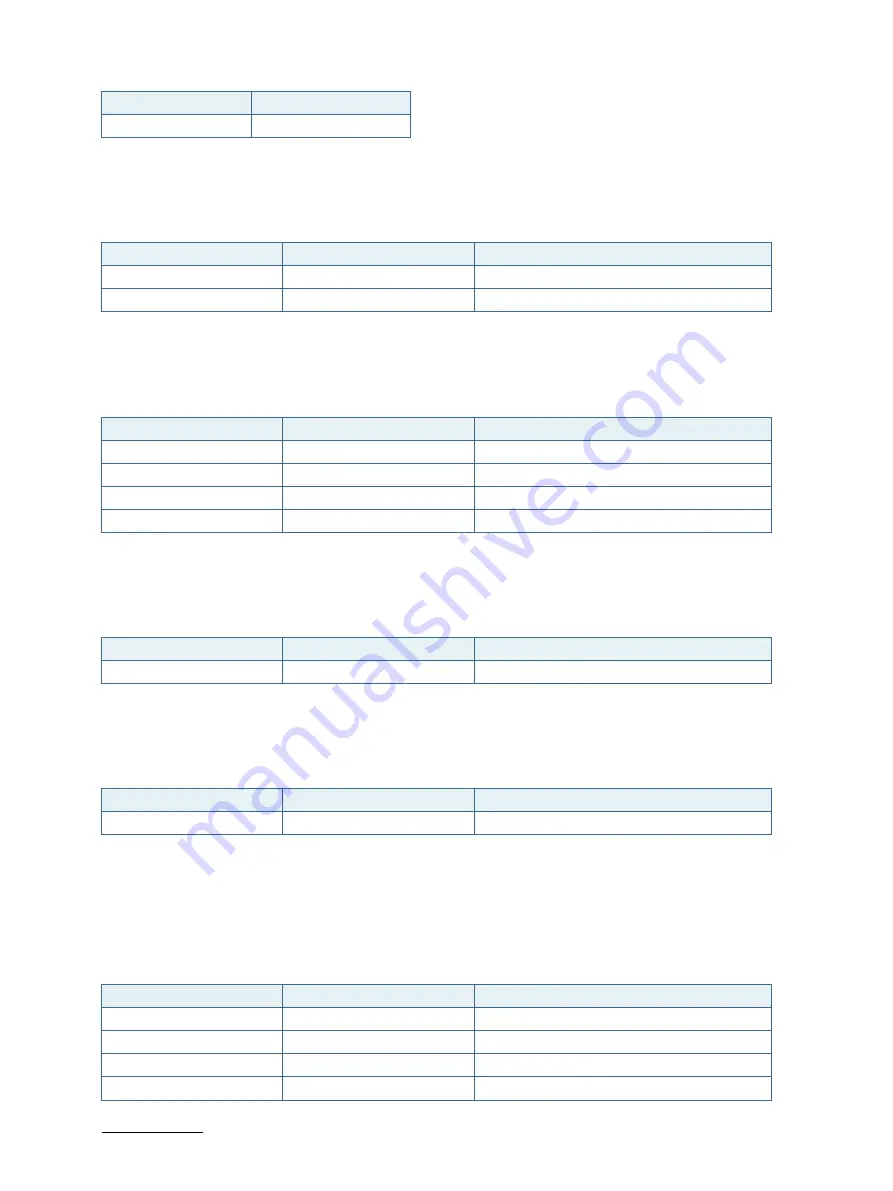

2.3.11.

Wake Signals

Table 24: Wake Signals

COMe Signal

SoC Pin

Description

WAKE0#

WAKE#/AGPIO2

passed through FPGA/EC

WAKE1#

AGPIO/SATEE_IFDET

passed through FPGA/EC

2.3.12.

Suspend Control

Table 25: Suspend Control

COMe Signal

SoC Pin

Description

SUS_STAT#/ESPI_RESET#

From FPGA

LPC_PD# signal might be used for SUS_STAT#

SUS_S3#

SOC_SLP_S3#

passed through FPGA

SUS_S4#

From FPGA

SUS_S5#

SOC_SLP_S5#

passed through FPGA

2.3.13.

Carrier Board Reset (CB_RESET#)

Table 26: Carrier Board Reset (CB_RESET#)

COMe Signal

SoC Pin

Description

CB_RESET#

SOC_PMU_RS T_1V8#

Output to carrier. Implemented in FPGA/EC

2.3.14.

System Reset (SYS_RESET#)

Table 27: System Reset (SYS_RESET#)

COMe Signal

SoC Pin

Description

SYS_RESET#

SOC_SYS_RESET#

Input from carrier. Passed through FPGA/EC

2.3.15.

External BIOS ROM Support/SPI

The Boot SPI0 is routed to COMe connector. BOM option allows general purpose SPI (GSPI0) to be connected to COMe

instead.

Table 28: External BIOS ROM Support

COMe Signal

SoC Pin

Description

SPI_CS#

SPI0_CS0# / SPI0_CS1#

SPI_CS# logic implemented in EC

SPI_MISO

SPI_MISO_1V8

Passed through Levelshifter SN74AVC4T774

SPI_MOSI

SPI_MOSI_1V8

Passed through Levelshifter SN74AVC4T774

SPI_CLK

SPI_CLK_1V8

Passed through Levelshifter SN74AVC4T774