COMe-cVR6 – User Guide Rev. 1.5

// 37

2.3.24.

PCI Express Graphics (3.0)

PCIe allows a reversal of the physical lane ordering between the host device and the target device. The requirements

are that the lanes are still sequentially ordered but can be logically reversed; for example, on a x4 GFX APU lane 3

connects to dGPU lane 0, APU lane 2 connects to dGPU lane1, APU lane 1 connects to dGPU lane 2, and APU lane 0

connects to dGPU lane 3.

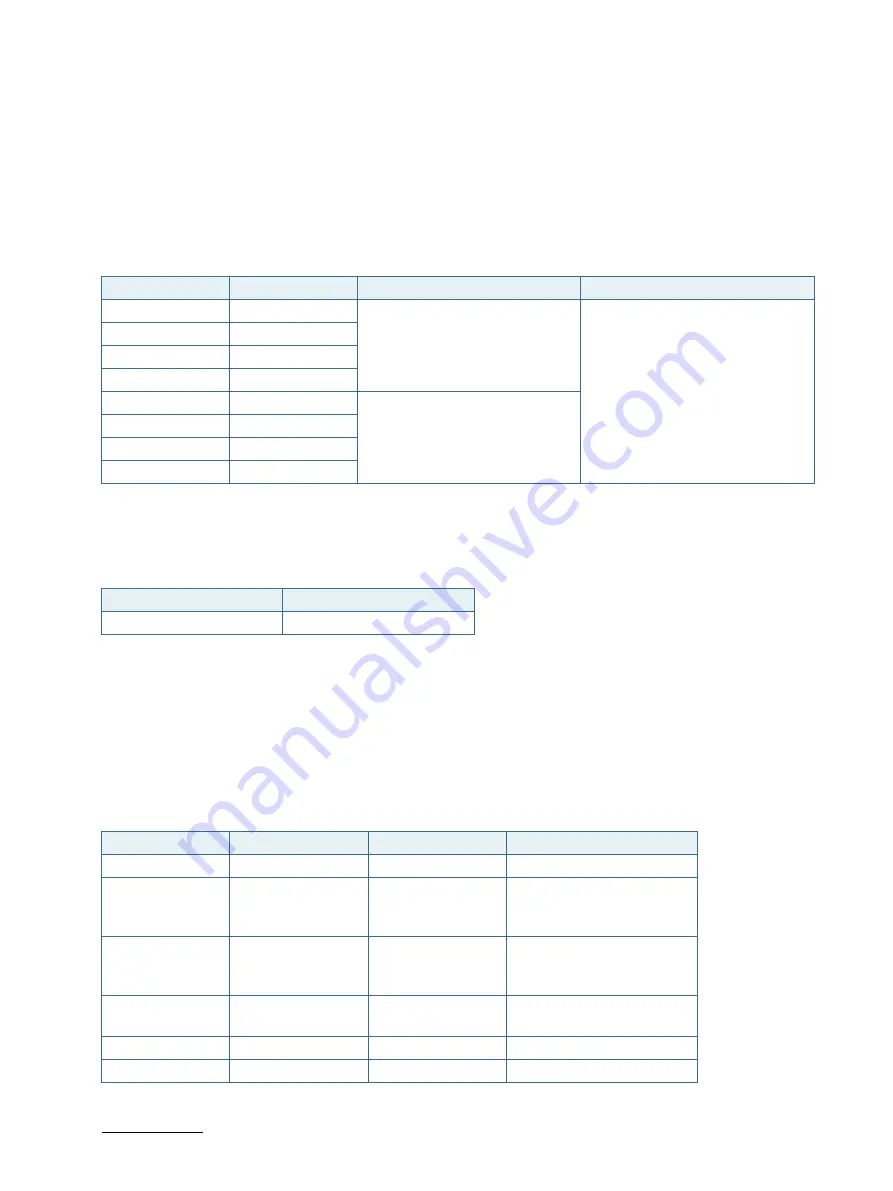

Table 40: PCI Express Graphics (3.0)

COMe connector

GPP Lane

Lane Config

PEG0

0

x4

x8

PEG1

1

PEG2

2

PEG3

3

PEG4

4

x4

PEG5

5

PEG6

6

PEG7

7

2.3.25.

PCI Express Reference Clock

Table 41: PCI Express Reference Clock

COMe Connector

SoC Pin

PCIE_CK_REF

GPP_CLK0

2.3.26.

USB

The SoC offers the following configurations:

Up to 4x USB 2.0 (8x USB 2.0 with Option USB-Hub)

Up to 3x USB 3.1 10 Gbit/s

1x USB 3.1 5 Gbit/s

Table 42: USB

COMe

SoC USB2

Hub (on Soc port 5)

SoC USB_SS

USB0/USB_SS0

USB_0_P1 (Port 1)

USB_C0_P1 (Port 1)

USB1/USB_SS1

USB_0_P2 (Port 2)

GEN2 (10 Gbit/s)

USB_C0_P2 (Port 2)

GEN2 (10 Gbit/s)

USB2/USB_SS2

USB_0_P3 (Port 3)

USB_C0_P3 (Port 3)

GEN2 (10 Gbit/s)

optional, shared with DDI3

USB3/USB_SS3

USB_1_P0 (Port 4)

USB_C1_P0 (Port 4) GEN1 (5

Gbit/s)

USB4

USB2_4 (Port 1)

USB5

-

USB2_5 (Port 2)