CP3005 – User Guide Rev. 1.8

// 46

Bitfield

Description

1 = TPM enabled

4

CRST

CPCI reset input when the CP3005 is in a peripheral slot:

0 = Disable CPCI reset to board

1 = Enable CPCI reset to board

2

SCOMA

COMA routing selection:

0 = Rear I/O

1 = Extension module

The reset value of the SCOMA bit depends on the board version ordered. If the CP3005 is

ordered as a rear I/O version, the reset value is 0. If the CP3005 is ordered as a front I/O

version, an automatic switch over to the 8HP extension module is processed per default.

4.3.5.

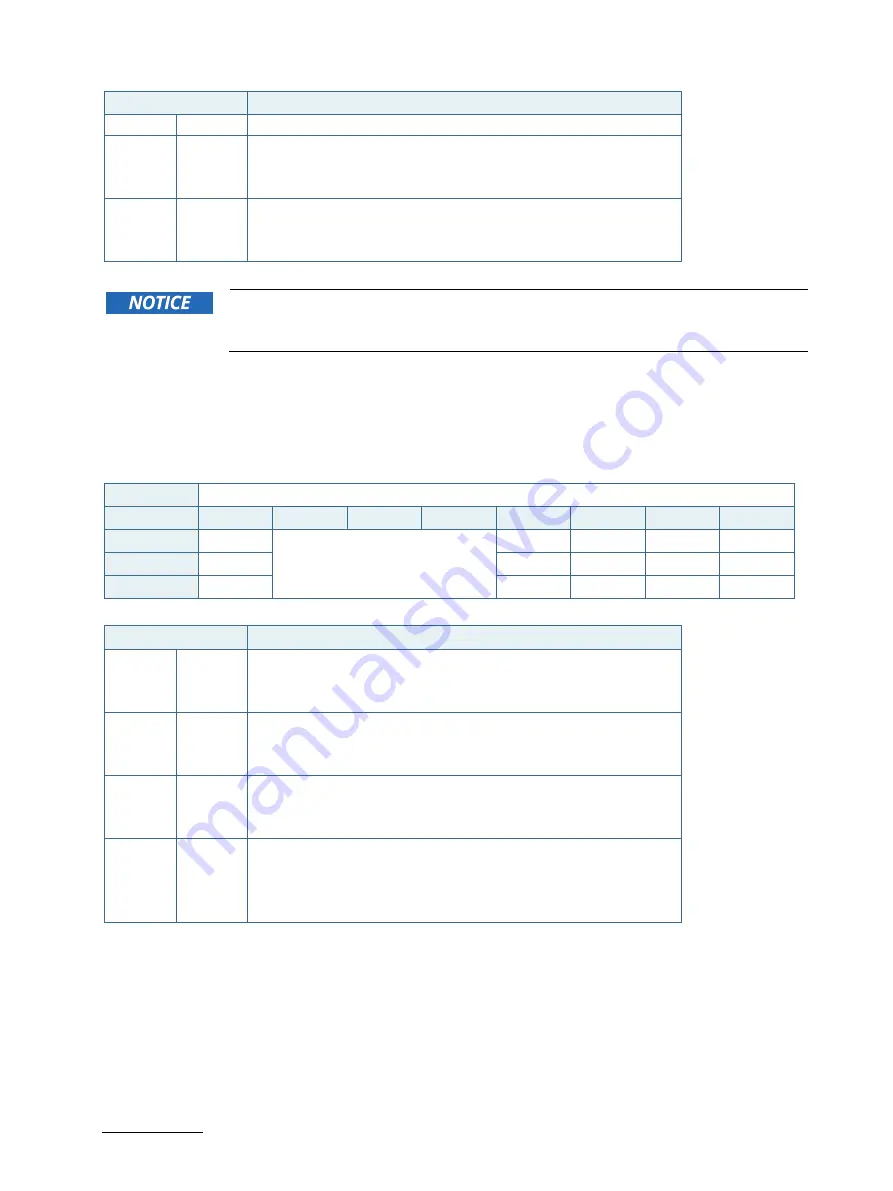

Device Protection Register (DPROT)

The Device Protection Register holds the write protect signals for non-volatile devices.

Table 23: Device Protection Register (DPROT)

Address

0x284

Bit

7

6

5

4

3

2

1

0

Name

SWP

Reserved

R

000

SFWP

JMP2

BSWP

SSWP

Access

R

R/W

R

R

R/W

Reset

0

0

0

0

0

Bitfield

Description

7

SWP

System write protection status:

0 = Onboard non-volatile memory devices not write protected

1 = Onboard non-volatile memory devices write protected

2

JMP2

System write protection via configuration resistors JMP2:

0 = System not write protected via JMP2

1 = System write protected via JMP2

1

BSWP

System write protection via backplane (SYS_WP#):

0 = System not write protected via backplane

1 = System write protected via backplane

0

SSWP

System write protection via software:

0 = System devices not write protected via software

1 = System write protected via software

Writing a ’1’ to this bit clears it. If this bit is set, it cannot be cleared.