- 24 -

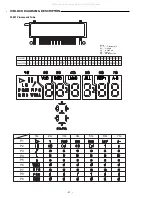

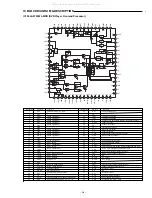

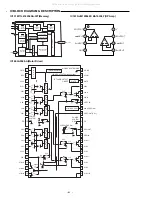

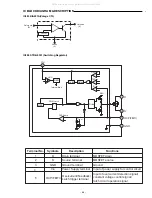

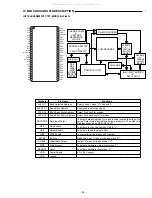

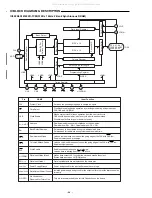

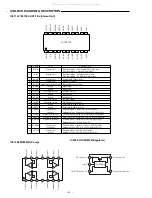

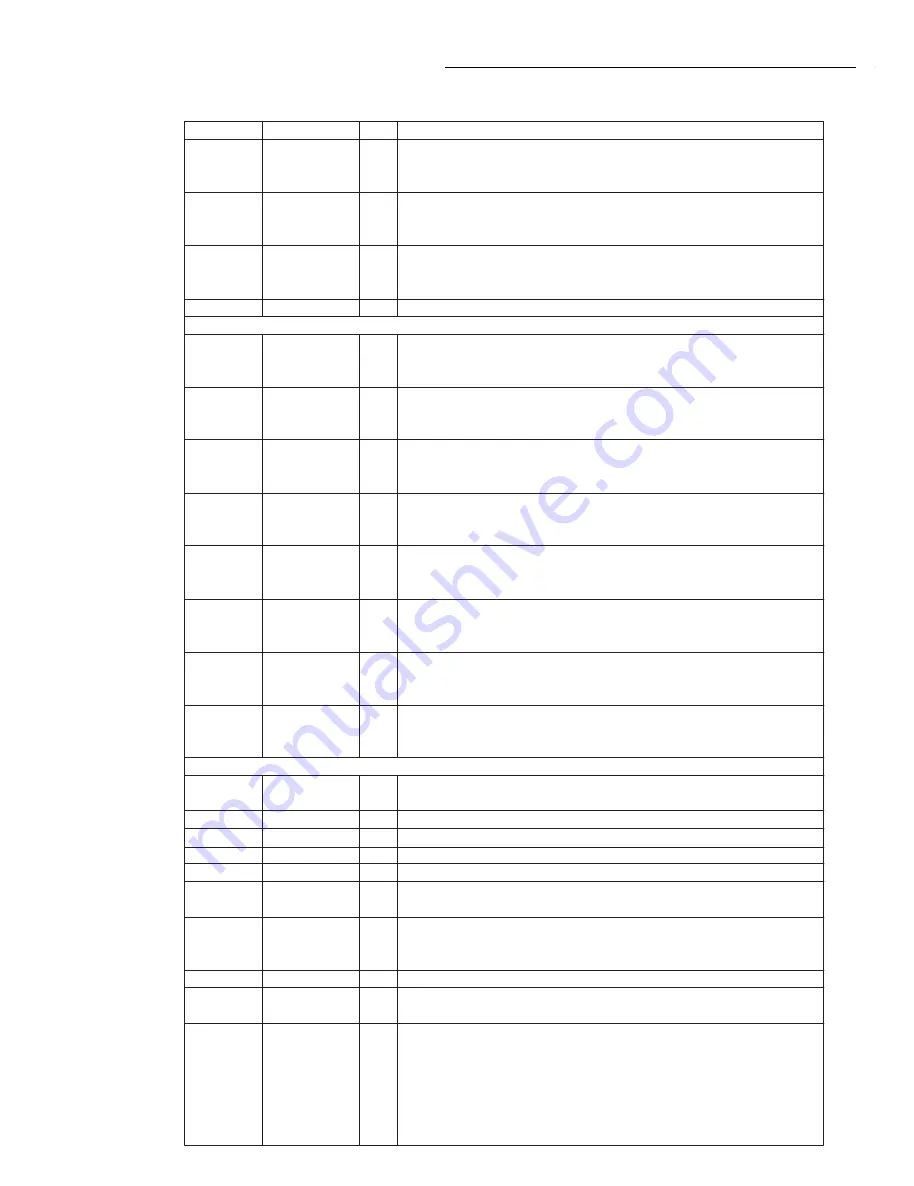

IC BLOCK DIAGRAM & DESCRIPTION

IC800 ZR36742(A/V Decoder)

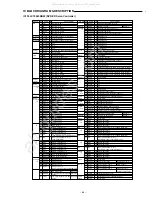

Function

YC O : Y signal O.

RGB O : R signal O.

YUV O : V signal O.

YC O : C signal O.

RGB O : B signal O.

YUV O : U sibnal O.

Which CVBS signal or C signal O.

Select be unrelated to YC / RGB / YUV mide.

DAC adjusting resistor connect.

ITU-R656 conform Y / C multiplex digital video O.

ADP ICE interface modo select I.

Controled general I / O by microcomputer software.

ITU-R656 conform Y / C multiplex digital video O.

ADP ICE interface data I.

Coutroled general I / O by microcomputer software.

ITU-R656 conform Y / C multiplex digital video O.

ADP ICE interface data O.

Controled general I / O by microcomputer software.

ITU-R656 conform Y / C multiplex digital video O.

ADP ICE interface clock I.

Controled general I / O by microcomputer software.

ITU-R656 conform Y / C multiplex digital video O.

CPU JTAG clock I.

Controled general I / O by microcomputer software.

ITU-R656 conform Y / C multiplex digital video O.

CPUJTAG tms I.

Controled general I / O by microcomputer software.

ITU-R656 conform Y / C multiplex digital video O.

CPUJTAG data I.

Probe UART data I.

ITU-R656 conform Y / C multiplex digital video O.

CPUJTAG data O.

Probe UART data O.

Audio master clock I / O.

128,192,256 or 384fs sampling frequency (Programable) use.

S / PDIF O.

N / C

Digital stereo audio serial data O.

Digital stereo audio serial data I.

Digital stereo audio bit clock O.

Palarity is programable.

Digital stereo audio LR clock O.

AOUT and AIN data output or latch, clock trailing edge or

last transition edge(programable).

Controled general I / O by ADP software.

27.000MHz clock I for audio master clock generating.

Connected to GCLK when usually operation.

Audio PLL set I.

Can change when RESET# signal assert.

Uqually operation : low RESET# signai assert term.

Controled general I / O by microcomputer softwaer.

Pin No.

172

173

170

175

Digital video port, CPU and ADP test (8 pin)

199

201

200

198

202

203

205

204

I/O

AO

AO

AO

AI

O#

I#

I/O

O#

I#

I/O

O#

O#

I/O

O#

I#

I/O

O#

I#

I/O

O#

I#

I/O

O#

I#

I

O#

O#

O

Name

Y/R/V

(DAC B)

C/B/U

(DAC C)

CVBS/C

(DAC D)

RSET

VID[7]#

ICETMS#

GPCI/O[22]

VID[6]#

ICETDI#

GPCI/O[23]

VID[5]#

ICETDO#

GPCI/O[24]

VID[4]#

ICETCK#

GPCI/O[25]

VID[3]

JTCK#

GPCI/O[46]

VID[2]#

JTMS#

GPCI/O[47]

VID[1]#

JTDI#

PUPRD

VID[0]#

JTDO#

PUPTD

Digital audio port (11 pin)

179

181

186,187

184

192

188

190

182

162

193

I/O

O

O

I

O

O

I/O

ID

ID#

I/O

AMCLK

S/PDIF

AOUT[2:1]

AOUT[0]

AIN

ALRCLK

ABCLK

GPAI/O

GCLK1

PLLCFGA#

GPCI/O[21]

All manuals and user guides at all-guides.com