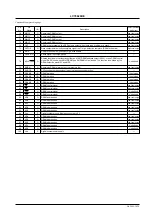

No. 5995-10/34

LC78626KE

Continued from preceding page.

Pin

Pin

I/O

Description

Output pin states

No.

Name

during reset

70

MMC0

O

Remaining DRAM output

Low-level output

71

MMC1

O

Remaining DRAM output

Low-level output

72

MMC2

O

Remaining DRAM output

Low-level output

73

MMC3

O

Remaining DRAM output

Low-level output

74

OVF

O

DRAM write terminated. (An RZP pulse is output when there is an overflow or a shock.)

Low-level output

75

CNTOK

O

Data contact point detection complete signal: low

→

high: detection complete. (DRAM write start).

High-level output

76

WOK

I

DRAM write enable signal input: high: write enable.

—

77

PAUSE IN

I

Pause signal input: high: pause.

—

78

AD10/CAS2

O

Undefined

79

EMPN

O

Remaining DRAM alarm output: low: memory low.

Low-level output

80

SHOCK

I

C2F shock detect pause signal input: low: pause shock detection.

—

81

DRAM3

I/O

DRAM data bus

Input mode

82

DRAM2

I/O

DRAM data bus

Input mode

83

DRAM1

I/O

DRAM data bus

Input mode

84

DRAM0

I/O

DRAM data bus

Input mode

85

OE

O

DRAM control signal

Low-level output

86

WE

O

DRAM control signal

High-level output

87

CAS

O

DRAM control signal

Undefined

88

RAS

O

DRAM control signal

Undefined

89

AD9

O

DRAM address bus

Low-level output

90

AD8

O

DRAM address bus

Low-level output

91

AD7

O

DRAM address bus

Low-level output

92

AD6

O

DRAM address bus

Low-level output

93

AD5

O

DRAM address bus

Low-level output

94

V

SS

P

Digital system ground. Must be connected to 0 V.

—

95

AD4

O

DRAM address bus

Low-level output

96

AD3

O

DRAM address bus

Low-level output

97

AD2

O

DRAM address bus

Low-level output

98

AD1

O

DRAM address bus

Undefined

99

AD0

O

DRAM address bus

Undefined

100

V

DD

P

Digital system power supply

—

Shared function pin that functions either as a 16M DRAM address output (AD10) or as a DRAM control

signal (CAS2) used when 8M of DRAM (two 4M DRAM chips) is used. The function is switched by the

DRAM selection pins MR1 and MR2.