*

When the desired number of tracks is entered as a binary number, the track check operation begins with the falling

edge of the RWC.

*

During the track check the TOFF pin becomes high and the tracking loop turns off, and thus there is the need to

provide a feed to the feed motor.

*

When the track check In/Out commands are entered, the WRQ signal changes from the subcode Q standby monitor

that it is during normal times to become the track check monitor. This signal becomes high when half of the number

of tracks have been checked, and becomes low when the check is complete. The microcontroller sees that the WRQ

signal has become low and determines that the check has been completed.

*

If the two-byte reset command is not entered, the track check operation begins again. In other words, if you wished to

advance 20,000 tracks, then a single 201 track check code would be sent and then when 100 cycles of the WRQ have

been counted, then there have been 20,000 track checks.

*

When the track check is performed, the brake command is used to lock the pickup to a track.

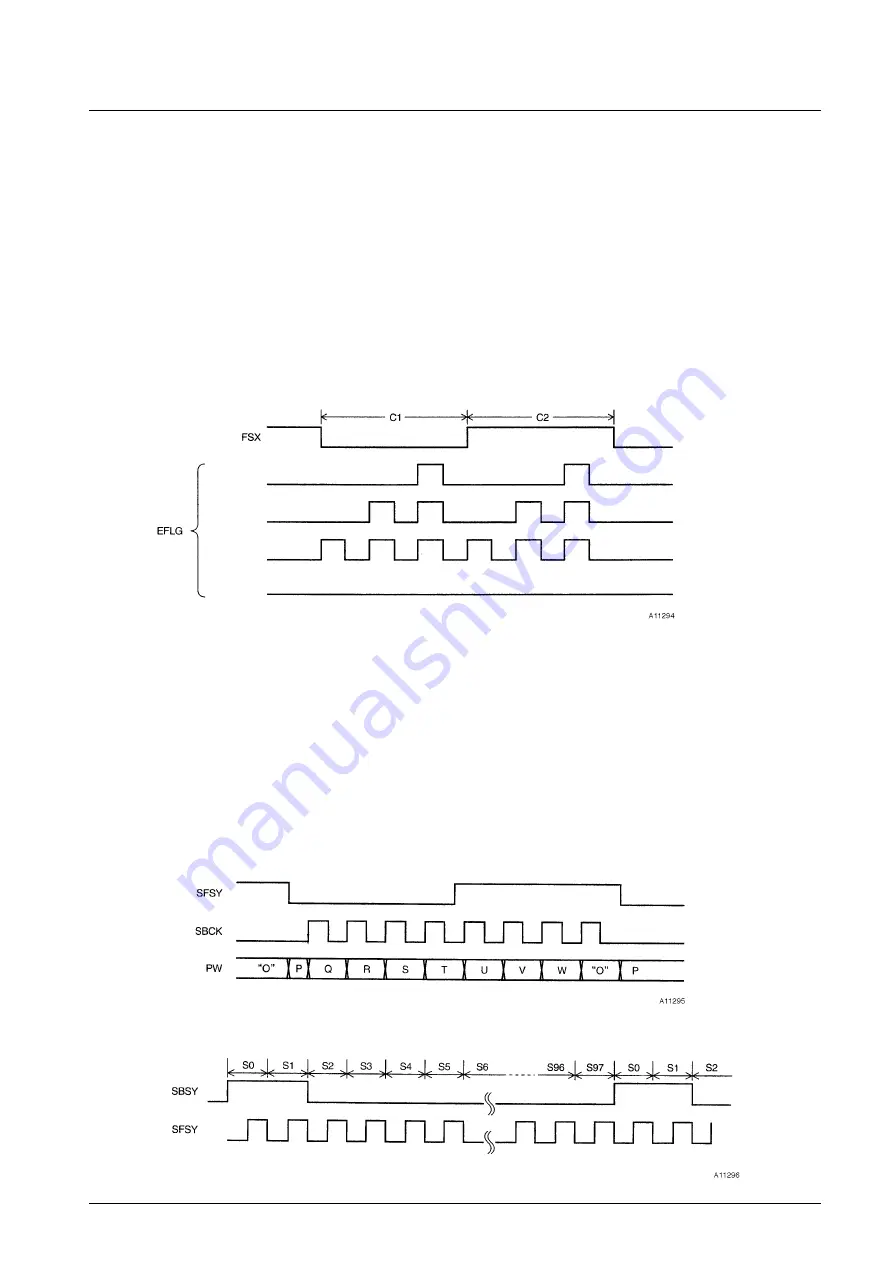

The Error Flag Output

Pin 43: EFLG, Pin 44: FSX

The FSX is the 7.35 kHz frame sync signal that is created by frequency dividing the crystal clock. For each frame, the

error correction status is output to EFLG. It is easy to tell the quality of the playback by the number of high pulses that

appear in the EFLG signal.

The Subcode P, Q and R to W Output Circuits Pin 34: SBCK, Pin 35: SFSY/CONT4, Pin 36: PW/CONT5, Pin 37: SBSY

PW is the subcode signal output pin. (Note: Pin 35 and Pin 36 are, respectively, a general I/O pin and an exclusively

shared pin, and the selection of the pin depends on commands from the micro controller. See the item “General I/O

Ports” on page 24.) By applying 8 clocks to SBCK within 136 µs of the falling edge of SFSY, it is possible to read all

codes until P, Q, and R to W. The signal that appears at the PW pin changes with the rising edge of SBCK. When no

clock is applied to SBCK, the “P” code is output to PW. SFSY is a signal that is output for each subcode frame, and the

falling edge of this signal indicates that the subcode symbol (P to W) output is in standby. The subcode data P is output at

the falling edge of this signal.

SBSY is a signal output for each subcode block. This signal becomes high during sync signals S0 and S1, and its falling

edge indicates the end of the subcode sync signal and the beginning of the data in subcode block (in EIAJ format).

No. 5995-19/34

LC78626KE

1 correction

2 correction

Correction

function

No errors