Bilingual Function

* At reset or when a stereo command ($28) has been entered, Lch and Rch are output, respectively, to Lch and Rch.

* When the Lch set command ($29) is entered, the Lch data is output to both Lch and Rch.

* When the Rch set command ($2A) is entered, the Rch data is output to both Lch and Rch.

Deemphasis Pin 45: EMPH

Of the subcode Q control data, the pre-emphasis on/off bit is output from the EMPH pin. When this pin is high, the

deemphasis circuit within this IC is activated, and the D/A converter output are de-emphasized.

Digital Attenuator

It is possible to apply digital attenuation to the audio data by setting the RWC high and inputting from the COIN a two

byte command synchronized with the CQCK clock.

After reset, the attenuation level is set to “MUTE” (the attenuation coefficient is 00H, where MUTE = –

∞

), and thus it is

necessary to directly set the attenuation coefficient EEH using the direct set (ATT DATA SET) command in order to

produce a sound. The attenuation level can be set to a range from 00H to EEH (239 different levels) by the

microcontroller commands.

This two byte command is different from the two byte commands used in track counting in that RWC only needs to be

set once, and it is not necessary to reset the two byte command either. (See the two byte command RWC1 set on page

13.)

After inputting the target attenuation level in terms of 00H to EEH, then if the attenuate step-up/step-down commands are

transmitted, the system steps closer to the target with the corresponding step size of 4, 8, or 16, synchronized with the

rising edge of LRSY. However, when the ATT DATA SET command has been used, then the target value is set directly.

When new data is entered during the transition, then the target value is approached from whatever value is in effect at

that time. Caution is required when using the step-up/step-down commands at this time.

No. 5995-21/34

LC78626KE

Code

COMMAND

RES = low

$28

STO CONT

●

●

$29

Lch CONT

$2A

Rch CONT

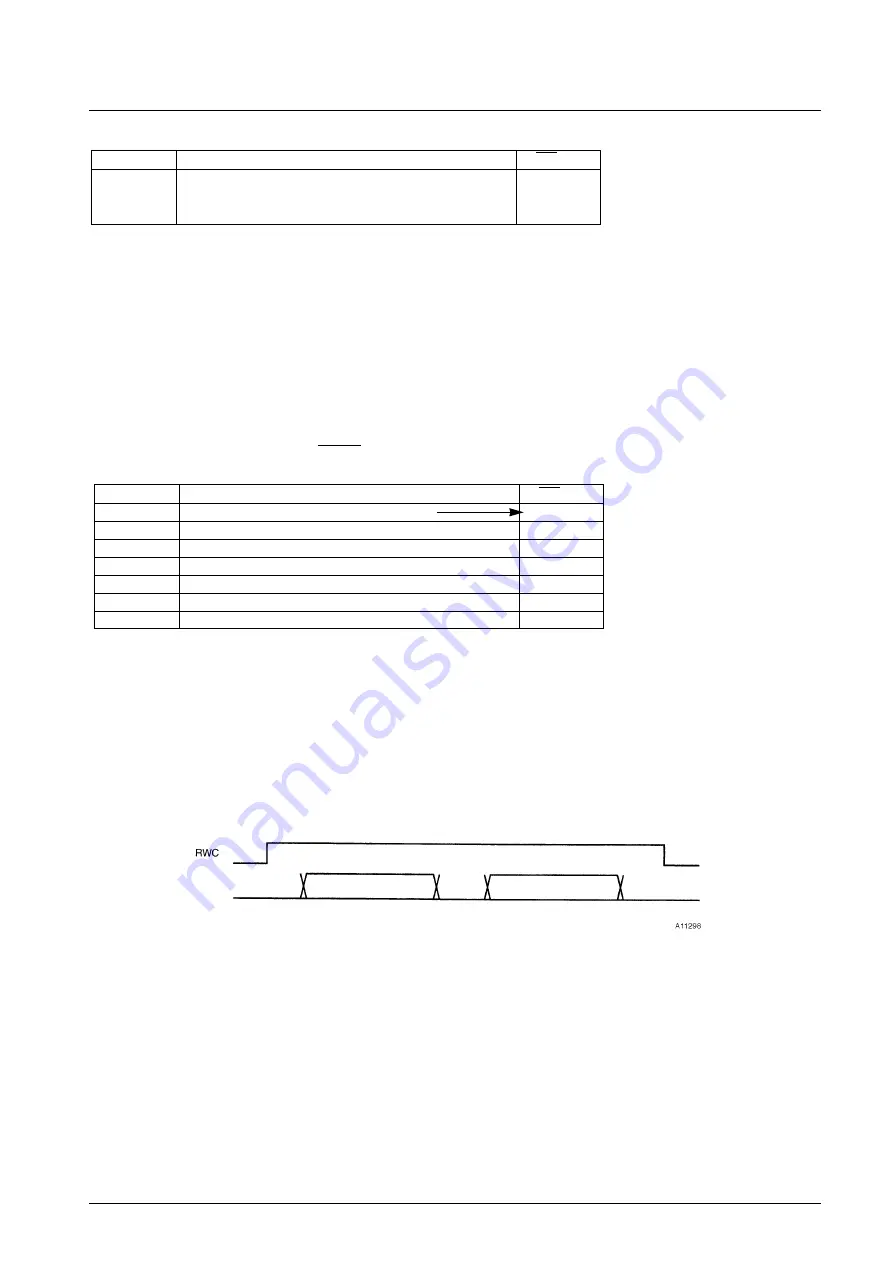

Code

COMMAND

RES = low

$81

ATT

DATA

SET

DATA 00H Set

$82

ATT

4STEP

UP

(MUTE –

∞

dB)

$83

ATT

4STEP

DOWN

$84

ATT

8STEP

UP

$85

ATT

8STEP

DOWN

$86

ATT

16STEP

UP

$87

ATT

16STEP

DOWN

Command

Attenuation data 00H to EEH

Attenuate set command