8

U3 LS188 (VCD ENCODE)

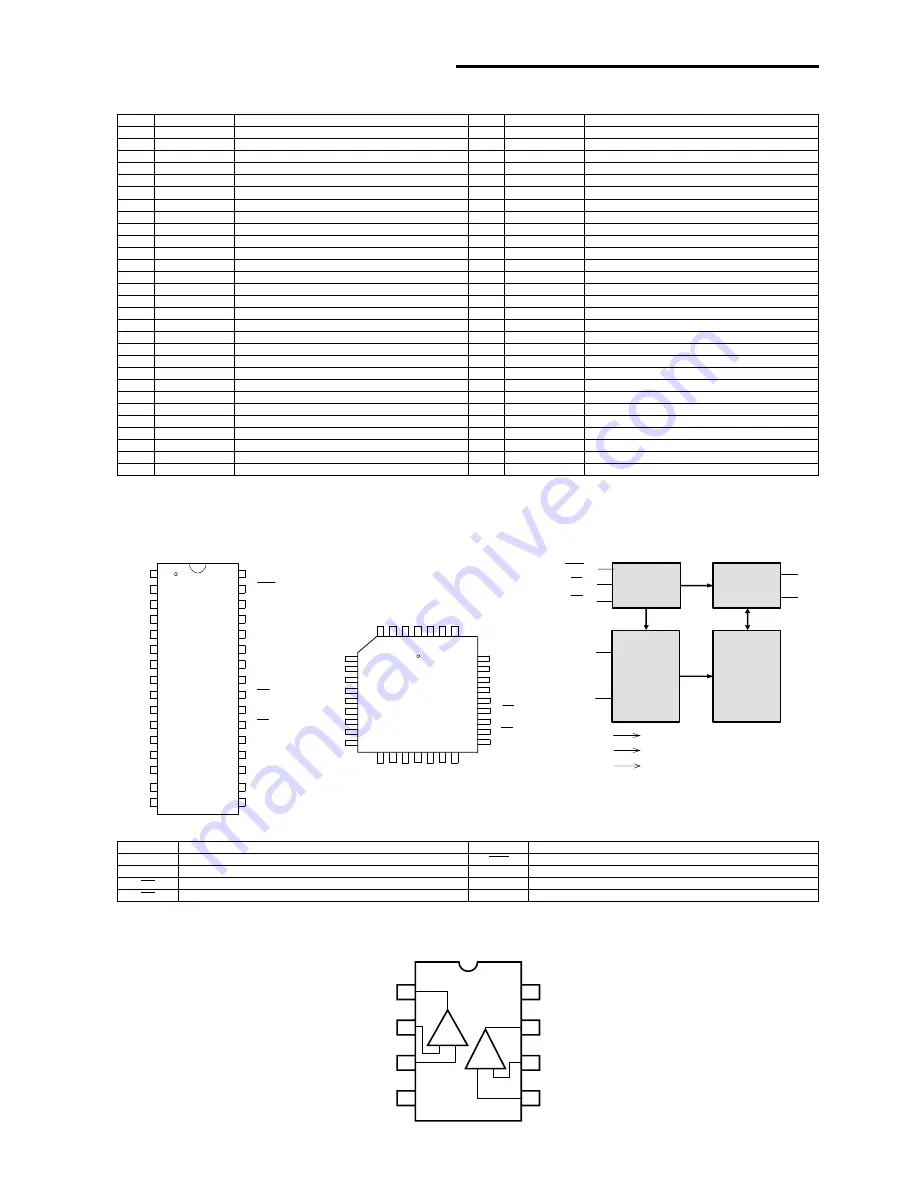

IC BLOCK DIAGRAM & DESCRIPTION

Symbol

Description

DR_D_10

DRAM Data Bus 10

GPIO_8

programmable I/O 8

CD_C2P0

CD data error flag input

DR_D_0

DRAM Data Bus 0

DR_D_15

DRAM Data Bus 15

DR_D_1

DRAM Data Bus 15

Pin

71

84

85

86

87

98

Symbol

Description

Pin

DR_D_14

88

DRAM Data Bus 14

VDD_IO_20

89

System I/O power supply

DR_D_2

90

DRAM Data Bus 2

DR_D_13

91

DRAM Data Bus 13

VSS_IO_20

92

System I/O ground

DR_D_3

93

DRAM Data Bus 3

DR_D_12

94

DRAM Data Bus 12

DR_D_4

95

DRAM Data Bus 4

DR_D_11

96

DRAM Data Bus 11

DR_D_5

97

DRAM Data Bus 5

GPIO_6

73

programmable I/O 6

GPIO_3

76

programmable I/O 3

GPIO_2

77

programmable I/O 2

GPIO_1

78

programmable I/O 1

GPIO_0

79

programmable I/O 0

IR_IN

80

IR input

CD_DATA

81

CD serial data input

CD_LRCK

82

CD Left/right Clock input

CD_BCK

83

CD bit Clock input

VSS_PLL_0

99

System PLL ground

VDD_PLL_0

100

System PLL power supply

DR_D_6

101

DRAM Data Bus 6

DR_D_9

102

DRAM Data Bus 9

DR_D_7

103

DRAM Data Bus 7

DR_D_8

104

DRAM Data Bus 8

VSS_CORE_20

105

System core ground

GPIO_5

74

programmable I/O 5

GPIO_4

75

programmable I/O 4

GPIO_7

72

programmable I/O 7

LCAS_L

106

Lower Column Address Strobe output

DR_WE_L

107

Memory Write Enable output

VDD_IO_30

108

System I/O power supply

UCAS_L

109

Upper Column Address strobe output

URAS_L

110

Upper row address strobe output

VSS_CORE_20

111

System core ground

LRAS_L

112

Lower row address strobe outputs

DR_A_8

113

DRAM Address bus outputs 8

DR_A_0

114

DRAM Address bus outputs 0

DR_A_7

115

DRAM Address bus outputs 7

DR_A_1

116

DRAM Address bus outputs 1

DR_A_6

117

DRAM Address bus outputs 6

VSS_IO_30

118

System I/O ground

DR_A_2

119

DRAM Address bus outputs 2

DR_A_5

120

DRAM Address bus outputs 5

VSS_CORE_30

121

System core ground

DR_A_3

122

DRAM Address bus outputs 3

DR_A_4

123

DRAM Address bus outputs 4

VDD_CORE_30

124

System core power supply

EMI_A_17

125

EMI Adress Bus Outputs 17

EMI_A_14

126

EMI Adress Bus Outputs 14

EMI_A_13

127

EMI Adress Bus Outputs 13

EMI_A_8

128

EMI Adress Bus Outputs 8

A6

A5

A4

A3

A2

A1

A0

Q0

5

6

7

8

9

10

11

12

13

Q

1

Q

2

Q

4

Q

5

Q

6

1

4

4 3 2 1 3

2

3

1

3

0

A14

A13

A8

A9

OE

A11

Q7

29

28

27

26

25

24

23

22

21

32-pin PLCC

G

N

D

1

5

1

6

1

7

1

8

1

9

2

0

1

7

V

c

c

CE

A10

Q5

OE

A10

Q7

Q6

A13

A8

A9

A11

PGM

A17

Q0

A0

A2

A3

A4

A5

A6

A7

A12

A15

A16

A14

A1

Vcc

Vpp

A

1

5

A

1

6

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

30

31

32

25

26

27

28

29

20

21

22

23

24

19

18

17

Q3

Q4

GND

Q2

CE

Q1

Q

3

A7

A

1

2

V

p

p

/

P

G

M

A

32-pin DIP

CONTROL

OUTPUT

BUFFER

DECODER

CORE

ARRAY

Q0

Q7

.

CE

OE

A0

.

PGM

V

GND

CC

V

PP

A17

+

+

1

2

3

4

8

7

6

5

OUT1

– IN1

+ IN1

V

EE

V

CC

OUT2

– IN2

+ IN2

1ch

2ch

–

–

U8 BA4510F (OPERATIONAL AMP)

U6 W27C020 (EPROM)

Symbol

Description

A0-A17

Address Inputs

Q0-Q7

Data Inputs/Outputs

CE

Chip Enable

OE

Output Enable

Symbol

Description

PGM

Program Enable

V

PP

Program/Erase Supply Voltage

V

CC

Power Supply

GND

Ground

Summary of Contents for VCD-X220

Page 2: ...18 19 17 16 S02 S01 10 9 8 4 3 1 2 5 6 7 12 13 14 15 11 1 EXPLODED VIEW ...

Page 12: ...11 WIRING CONNECTION MAIN PCB KEY PCB CD MECHANISM LCD DISPLAY DESCRIPTION ...

Page 14: ...13 SCHEMATIC DIAGRAM MAIN PCB 1 2 ...

Page 15: ...14 SCHEMATIC DIAGRAM MAIN PCB 1 2 TO KEY PCB ...

Page 16: ...15 SCHEMATIC DIAGRAM MAIN PCB 2 2 ...

Page 17: ...16 SCHEMATIC DIAGRAM MAIN PCB 2 2 ...

Page 18: ...17 CN901 SCHEMATIC DIAGRAM KEY PCB ...

Page 19: ...18 SW2 J2 J3 WIRING DIAGRAM MAIN PCB TOP VIEW ...

Page 20: ...19 WIRING DIAGRAM MAIN PCB BOTTOM VIEW ...

Page 21: ...20 WIRING DIAGRAM KEY PCB TOP VIEW BOTTOM VIEW ...

Page 22: ...SANYO Electric Co Ltd Osaka Japan Mar 03 Printed in China ...